## ST.ANNE'S

#### COLLEGE OF ENGINEERING AND TECHNOLOGY

(Approved by AICTE, New Delhi. Affiliated to Anna University, Chennai)

(An ISO 9001: 2015 Certified Institution)

ANGUCHETTYPALA YAM, PANRUTI – 607 106.

# DEPARTMENT OF ELECTRONICS AND COMMUNICATION ENGINEERING

#### LAB MANUAL

SUBJECT CODE/NAME: EC 8661/VLSI DESIGN LABORATORY

YEAR/SEM: III/VI

AS PER ANNA UNIVERSITY, CHENNAI REGULATION 2017

#### **OBJECTIVES:**

#### The student should be made:

- To learn Hardware Descriptive Language(Verilog/VHDL)

- To learn the fundamental principles of VLSI circuit design in digital and analog domain

- To familiarize fusing of logical modules on FPGAs

- To provide hands on design experience with professional design (EDA) platforms

#### LIST OF EXPERIMENTS:

#### Part I: Digital System Design using HDL & FPGA (24 Periods)

- Design an Adder (Min 8 Bit) using HDL. Simulate it using Xilinx/Altera Software and

- implement by Xilinx/Altera FPGA

Design a Multiplier (4 Bit Min) using HDL. Simulate it using Xilinx/Altera Software and implement by Xilinx/Altera FPGA

Design an ALU using HDL. Simulate it using Xilinx/Altera Software and implement by 2.

- 3.

- 4.

- Xilinx/Altera FPGA

Design a Universal Shift Register using HDL. Simulate it using Xilinx/Altera Software and implement by Xilinx/Altera FPGA

Design Finite State Machine (Moore/Mealy) using HDL. Simulate it using Xilinx/Altera Software and implement by Xilinx/Altera FPGA

Note: Altera Software and implement.

- Design Memories using HDL. Simulate it using Xilinx/Altera Software and implement by Xilinx/Altera FPGA

Compare pre synthesis and post synthesis simulation for experiments 1 to 6. Requirements: Xilinx ISE/Altera Quartus/ equivalent EDA Tools along with Xilinx/Altera/equivalent FPGA Boards

#### Part-II Digital Circuit Design (24 Periods)

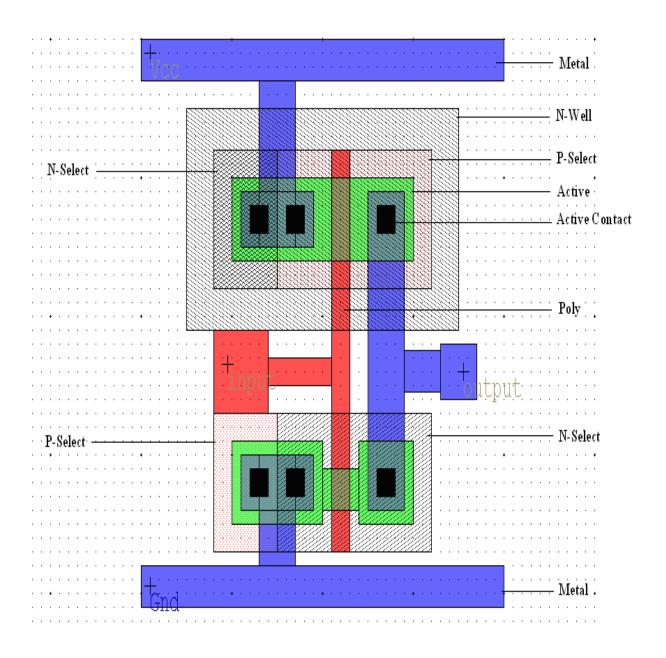

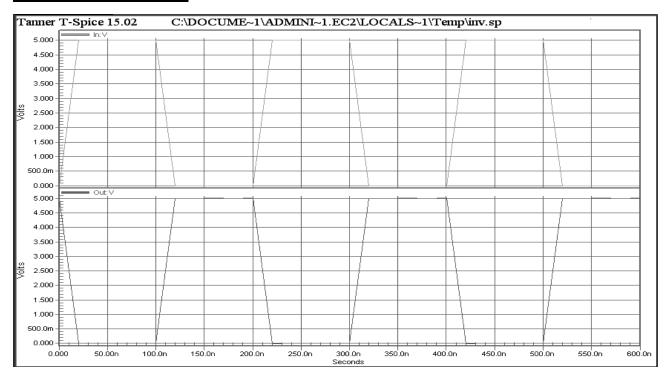

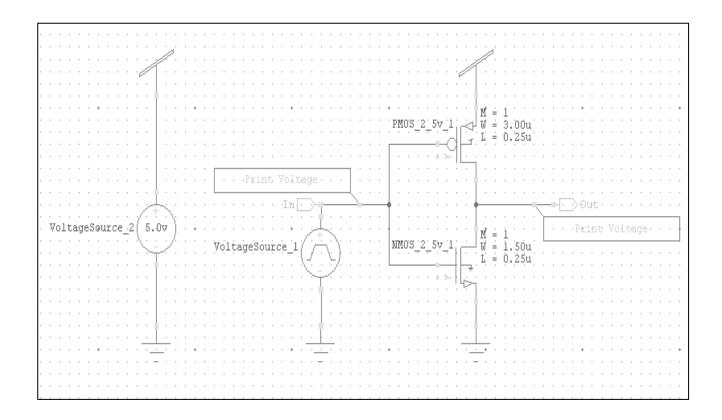

- Design and simulate a CMOS inverter using digital flow

- Design and simulate a CMOS Basic Gates & Flip-Flops

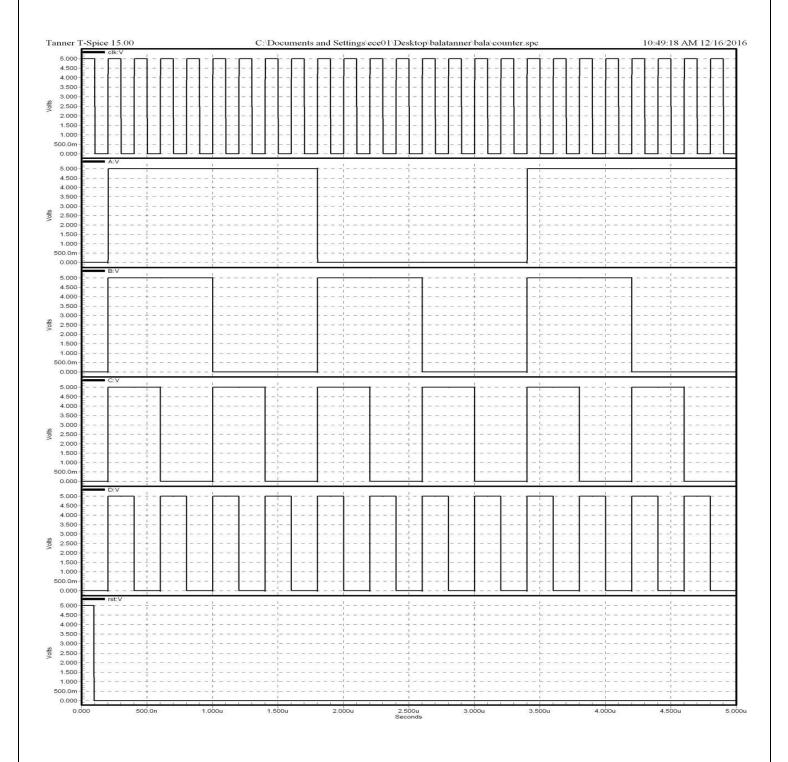

- Design and simulate a 4-bit synchronous counter using a Flip-Flops Manual/Automatic Layout Generation and Post Layout Extraction for experiments 7 to 9

#### Part-III Analog Circuit Design (12 Periods)

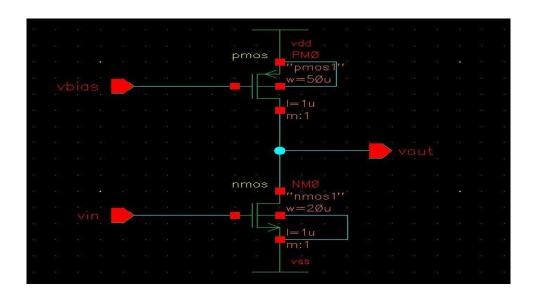

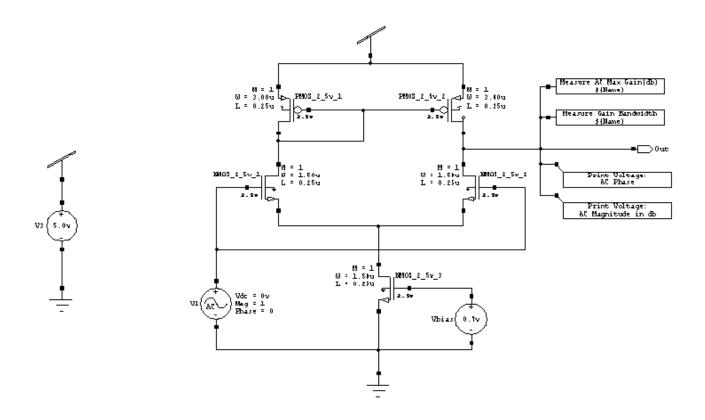

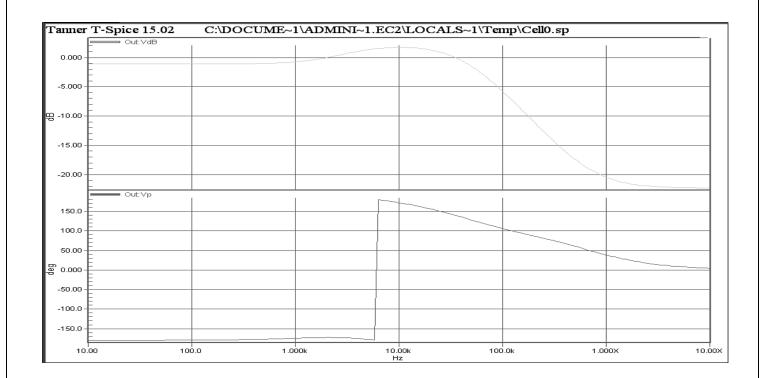

- 10. Design and Simulate a CMOS Inverting Amplifier.

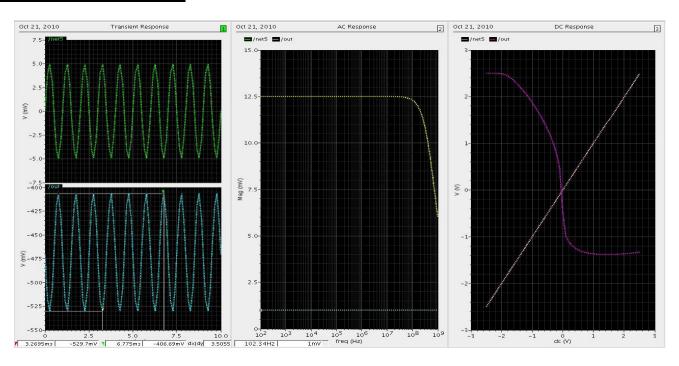

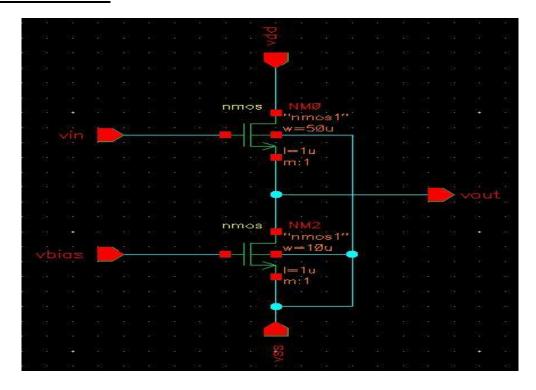

- 11. Design and Simulate basic Common Source, Common Gate and Common Drain Amplifiers. Analyze the input impedance, output impedance, gain and bandwidth for experiments 10 and 11 by performing Schematic Simulations.

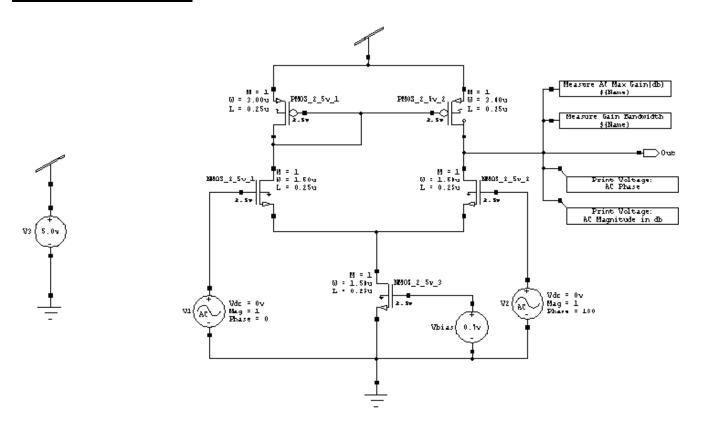

- 12. Design and simulate simple 5 transistor differential amplifier. Analyze Gain, Bandwidth and CMRR by performing Schematic Simulations.

Requirements: Cadence/Synopsis/ Mentor Graphics/Tanner/equivalent EDA Tools

**TOTAL: 60 PERIODS**

#### LAB PLAN

#### LIST OF EXPERIMENTS

#### **CYCLE-I**

- 1. Design an Adder (Min 8 Bit) using HDL. Simulate it using Xilinx/Altera Software and implement by Xilinx/Altera FPGA

- 2. Design a Multiplier (4 Bit Min) using HDL. Simulate it using Xilinx/Altera Software and implement by Xilinx/Altera FPGA

- 3. Design an ALU using HDL. Simulate it using Xilinx/Altera Software and implement by Xilinx/Altera FPGA

- 4. Design a Universal Shift Register using HDL. Simulate it using Xilinx/Altera Software and implement by Xilinx/Altera FPGA

- 5. Design Finite State Machine (Moore/Mealy) using HDL. Simulate it using Xilinx/Altera Software and implement by Xilinx/Altera FPGA

- 6. Design Memories using HDL. Simulate it using Xilinx/Altera Software and implement by Xilinx/Altera FPGA

#### **CYCLE-II**

- 7. Design and simulate a CMOS inverter using digital flow

- 8. Design and simulate a CMOS Basic Gates & Flip-Flops

- 9. Design and simulate a 4-bit synchronous counter using a Flip-Flops

- 10. Design and Simulate a CMOS Inverting Amplifier.

- 11. Design and Simulate basic Common Source, Common Gate and Common Drain Amplifiers.

- 12. Design and simulate simple 5 transistor differential amplifier. Analyze Gain, Bandwidth and CMRR by performing Schematic Simulations.

Requirements: Cadence/Synopsis/ Mentor Graphics/Tanner/equivalent EDA Tools

# XILINX

TOOLS

| EXP.NO: | STUDY OF SIMULATION TOOLS |

|---------|---------------------------|

| DATE:   | STODION SIMILATION TOOLS  |

To study simulation tools using Xilinx software tool.

#### **TOOLS REQUIRED:**

#### Software:

1. Xilinx ISE Design Suite 12.1

#### **PROCEDURE:**

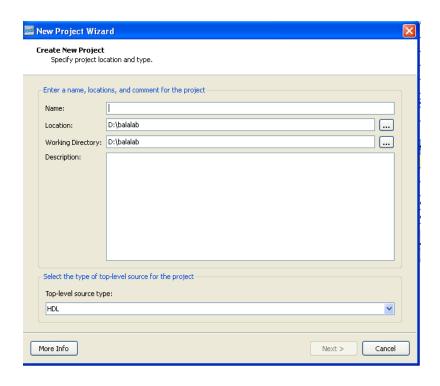

- 1. Now start the Xilinx ISE Design Suite 12.1

- 2. Go to file and click new project

- 3. Enter the project name and click next

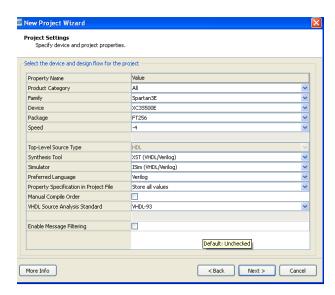

- 4. Select the family name is Spartan 3E, speed is -4 and simulator is verilog click next and click Finish.

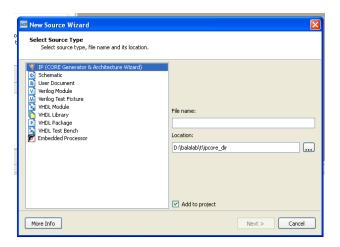

- 5. Click new source.

- 6. Select verilog module and type file name and click next.

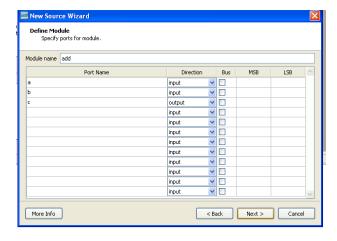

- 7. Assign input and output port and click next.

- 8. Finally the report is shown click finish.

- 9. Type the program save and click synthesis.

- 10. To see the output wave form change the source from implementation to simulation and click simulator behavior model in IS im simulator.

- 11. Give values to the input variables and then click run

- 12. In wave window, click run icon and you can see corresponding output.

#### **Steps to use Xilinx tool:**

Start the Xilinx Project Navigator by using the desktop shortcut or by using the

➤ Start → Programs → Xilinx ISE → Project Navigator.

➤ In the Project Navigator window go to FILE →New project→ Click on new source→ verilog module and give the name inverter.v →Define ports→Finish

➤ Select devices → General purpose → Spartan 3 → ISE simulator → verilog

In the create new source window select source type as verilog module give file name

$\triangleright$  assign inputs and outputs  $\rightarrow$  click next  $\rightarrow$  finish  $\rightarrow$  yes  $\rightarrow$  next  $\rightarrow$  next  $\rightarrow$  finish

➤ Double click on source file → complete the verilog code for inverter

- > Check syntax, and remove errors if present

- ➤ Simulate the design using ISE Simulator Highlight **inverter.v** file in the Sources in Project window. To run the Behavioral Simulation, Click on the symbol of FPGA device and then right click→Click on new source→Click on verilog text fixture→Give file name with \_tb→ finish

- ➤ Generate test bench file after initial begin assign value for inputs → Click on simulate behavioral model → see the output.

**RESULT:**

| EXP.NO: | STUDY OF SYNTHESIZE TOOLS |

|---------|---------------------------|

| DATE:   | STODION SINTINESIZE TOOLS |

To study synthesize tools using Xilinx software tool.

#### **TOOLS REQUIRED:**

Software:

1. Xilinx ISE Design Suite 12.1

#### THEORY:

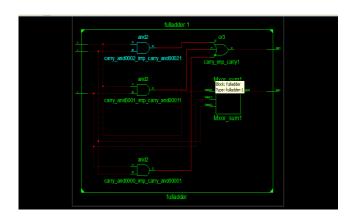

Synthesis is an automatic method of converting a higher level abstraction to a lower level abstraction. The synthesis tool convert **Register Transfer Level** (RTL) description to **gate level netlists**. These gate level netlists consist of interconnected gate level macro cells. These gate level netlists currently can be optimized for **area**, **speed** etc., The analyzed design is synthesized to a library of components, typically gates, latches, or flipflops. Hierarchical designs are synthesized in bottom up fashion, that is lower level components are synthesized before higher level components. Once the design is synthesized we have a gate level netlist. This gate level netlist can be simulated. Delay for the individual components are available as part of the description of the component libraries. Timing accurate simulation is not possible at this point because the actual timing characteristics is determined by the physical placement of the design within the FPGA chip. However, the functional simulation that is possible at this point is quite a bit more accurate than simulation based on user specified delays. After run the synthesize in process window then full adder model is converted to **netlist file**.

#### To convert the RTL to gates, three steps typically occur:

- \* The RTL description is translated to an unoptimized boolean description usually consisting of primitive gates such as AND and OR gates, flip-flop, and latches. This is a functionally correct but completely unoptimized description.

- \* Boolean optimization algorithms are executed on this boolean equivalent description to produce an optimized boolean equivalent description.

- \* This optimized boolean equivalent description is mapped to actual logic gate by making use of a technology library of the target process.

#### **PROCEDURE:**

- 1. Now start the Xilinx ISE Design Suite 12.1

- 2. Go to file and click new project

- 3. Enter the project name and click next

- 4. Select the family name is Spartan 3E, speed is -4 and simulator is verilog click next and click Finish.

- 5. Click new source.

- 6. Select verilog module and type file name and click next.

- 7. Assign input and output port and click next.

- 8. Finally the report is shown click finish.

- 9. Type the program save and click synthesis.

- 10. Go to synthesis → View RTL schematic

#### **PROGRAM:**

```

module full_adder (a,b,c,sum,carry);

output sum,carry ;

input a,b,c ;

assign sum = a ^ b ^ c;

assign carry = (a&b) | (b&c) | (c&a);

end module

```

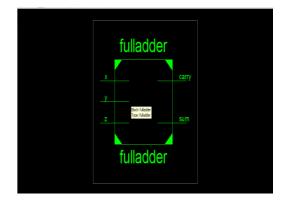

#### **RTL SCHEMATIC:**

#### **RESULT:**

| EXP.NO: | PLACE AND ROOT AND BACK ANNOTATION FOR FPGAS  |

|---------|-----------------------------------------------|

| DATE:   | T LACE AND ROOT AND DACK ANNOTATION FOR FIGAS |

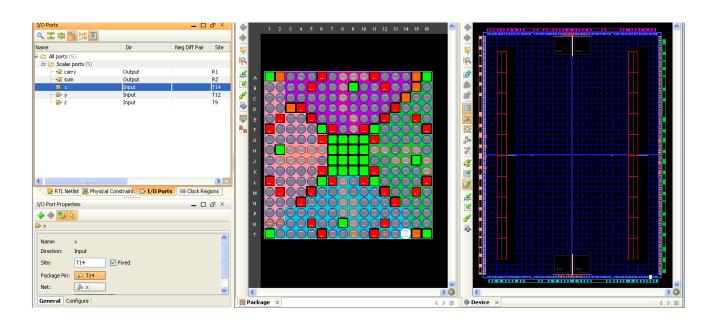

To study place and root and back annotation for FPGAs synthesize tools using Xilinx software tool.

#### **TOOLS REQUIRED:**

Software:

1. Xilinx ISE Design Suite 12.1

#### THEORY:

To map this Full adder design onto the FPGA. The primitive hardware elements that are available in Xilinx xc3s500e chip, namely lookup tables and positive-edge-triggered flip-flops are organized as a **two dimensional array of CLBs**. The net list from synthesize is composed of **gates, latches, and flip-flops**. It is necessary to assign CLB to net list primitives. This is the process of **mapping** a design. For example gates will be assigned to look-up tables. This process effectively translates the gate level netlist produce by the synthesize compiler into a netlist of FPGA primitive hardware components. Each elements of this new netlist corresponds to a hardware primitive in the FPGA Chip. The mapped design produces identifies the set of FPGA hardware primitives and their interconnection. The next step is to assign each of the components in the netlist to a equivalent physical primitives on the FPGA chip. Once this assignment or placement is made the interconnection between the components in the netlist must be made within the chip. This will require routing signals through the switch matrix and other inter connect resources available on FPGA Chip. This Place and route layout was generated from Xilinx ISE **Floor planner**. After place and route the design can be simulated to validate the design. At this point timing is more accurate because the propagation delays along routed signals and through CLBs can be more accurately estimated. This is particularly important for designs that are operating under tight timing tolerance.

#### To convert the RTL to gates, three steps typically occur:

- \* The RTL description is translated to an unoptimized boolean description usually consisting of primitive gates such as AND and OR gates, flip-flop, and latches. This is a functionally correct but completely unoptimized description.

- \* Boolean optimization algorithms are executed on this boolean equivalent description to produce an optimized boolean equivalent description.

- \* This optimized boolean equivalent description is mapped to actual logic gate by making use of a technology library of the target process.

#### **PROCEDURE:**

- 1. Now start the Xilinx ISE Design Suite 12.1

- 2. Go to file and click new project

- 3. Enter the project name and click next

- 4. Select the family name is Spartan 3E, speed is -4 and simulator is verilog click next and

click Finish.

- 5. Click new source.

- 6. Select verilog module and type file name and click next.

- 7. Assign input and output port and click next.

- 8. Finally the report is shown click finish.

- 9. Types the program saves and clicks synthesis.

10. Choose Implementation  $\rightarrow$  user constraints  $\rightarrow$  I/O pin planning (plan ahead) pre-synthesis, type the input /output port.

#### **PROGRAM:**

```

module full_adder (a,b,c,sum,carry);

output sum,carry ;

input a,b,c ;

assign sum = a ^ b ^ c;

assign carry = (a&b) | (b&c) | (c&a);

end module

```

#### **RESULT:**

| EXP.NO: | STUDY OF FPGA BOARD AND ON-BOARD LED'S AND |

|---------|--------------------------------------------|

| DATE:   | SWITCHES                                   |

To Study Field Programmable Gate Array (FPGA) board and to test the on-board LEDs and Switches using Xilinx software tool.

#### **TOOLS REQUIRED:**

Software:

1. Xilinx ISE Design Suite 12.1

#### THEORY:

#### **DIP SWITCHES:**

When in the UP or ON position, a switch connects the FPGA pin to  $V_{cc}$ , a logic High. When DOWN or in the OFF position, the switch connects the FPGA pin to ground, a logic low. The switches typically exhibit about 2ms of mechanical bounce and there is no active debouncing circuitry, although such circuitry could easily be added to the FPGA design programmed on the board.

#### **KEY SWITCHES:**

The key switches can provide pulse input to the FPGA. The switches connect to an associated FPGA pin. Pressing a key generates logic High on the associated FPGA pin. There is no active debouncing circuitry on the key switches.

#### LEDS:

Test LEDs are provided for mapping output of FPGA or tracking particular stage in the design. A series current limiting resistor of 270 ohm is associated with every LED. To turn on an individual LED, drive the associated FPGA control signal High.

#### **PROCEDURE:**

- 1. Create a new project & create a new Verilog file.

- 2. Type the program for testing LEDs and Switches and Save it

- 3. Synthesize the program and view the RTL Model.

- 4. Create test bench waveform and simulate it.

- 5. Download the program using the procedure given below into the FPGA.

- 6. Now test the physical working of the switches and the LED's on board.

#### **DOWNLOADING PROCEDURE:**

- 1. Select "Synthesis/Implementation" in the source window.

- 2. Select the created module (\*.v file) in the source window.

- 3. Select "user constraint" in the process window, double click "edit constraint" to create user constraint file (\*.UCF).

- 4. Type the net list to define the I/O pins and save it.

- 5. Double click "implement design" in the process window.

- 6. Double click "Generate programming "file and select the respective created bit file (\*.bit)

- 7. Double click "configure device (iMPACT)". In the impact window that appears, select 'configure device using boundary scan'. Click finish

- **8.** Right click on the created Xilinx model & select 'program', give OK on the displayed window.

#### **PROGRAM:**

```

module leds(a, b);

input [0:15]a;

output [0:15]b;

reg [0:15]b;

always@(a)begin

b=~a;

end

endmodule

```

| EXP.NO: | SIMULATION OF BASIC LOGIC GATES |

|---------|---------------------------------|

| DATE:   |                                 |

| ATRE    |                                 |

To write a verilog program for basic logic gates to synthesize and simulate using Xilinx software tool.

#### **TOOLS REQUIRED:**

Software:

1. Xilinx ISE Design Suite 12.1

#### THEORY:

#### **AND GATE:**

An AND gate is a digital logic gate with two or more inputs and one output that performs logical conjunction. The output of an AND gate is true only when all of the inputs are true. If one or more of an AND gate's inputs are false, then the output of the AND gate is false.

| EQUATION  | LOGIC SYMBOL | Т | TRUTH TABLE |  |

|-----------|--------------|---|-------------|--|

|           |              | A | В           |  |

| Y = a & b |              |   |             |  |

|           |              |   |             |  |

|           |              |   |             |  |

|           |              |   |             |  |

#### **OR GATE:**

An OR gate is a digital logic gate with two or more inputs and one output that performs logical disjunction. The output of an OR gate is true when one or more of its inputs are true. If all of an OR gate's inputs are false, then the output of the OR gate is false

| EQUATION       | LOGIC SYMBOL | TRUTH TABLE |   | LE |

|----------------|--------------|-------------|---|----|

|                |              | A           | В |    |

| $Y = a \mid b$ |              |             |   |    |

| _              |              |             |   |    |

|                |              |             |   |    |

|                |              |             |   |    |

#### **NOT GATE:**

A NOT gate, often called an inverter, is a nice digital logic gate to start with because it has only a single input with simple behavior. A NOT gate performs logical negation on its input. In other words, if the input is true, then the output will be false. Similarly, a false input results in a true output.

| EQUATION | LOGIC SYMBOL | TRUTH TABLE |

|----------|--------------|-------------|

|          |              | A           |

| Y = ~a   |              |             |

|          |              |             |

|          |              |             |

|          |              |             |

#### **NAND GATE:**

A NAND gate (sometimes referred to by its extended name, Negated AND gate) is a digital logic gate with two or more inputs and one output with behavior that is the opposite of an AND gate. The output of a NAND gate is true when one or more, but not all, of its inputs are false. If all of a NAND gate's inputs are true, then the output of the NAND gate is false.

| EQUATION     | LOGIC SYMBOL | TRUTH TABLE |   |   |

|--------------|--------------|-------------|---|---|

|              |              | A           | В | Y |

| Y = ~(a & b) |              |             |   |   |

|              |              |             |   |   |

|              |              |             |   |   |

#### **NOR GATE:**

A NOR gate (sometimes referred to by its extended name, Negated OR gate) is a digital logic gate with two or more inputs and one output with behavior that is the opposite of an OR gate. The output of a NOR gate is **true** all of its inputs are **false**. If one or more of a NOR gate's inputs are **true**, then the output of the NOR gate is **false**.

| EQUATION                                         | LOGIC SYMBOL | TRUTH TABLE |   | LE |

|--------------------------------------------------|--------------|-------------|---|----|

|                                                  |              | A           | В | Y  |

| $\mathbf{Y} = \sim (\mathbf{a} \mid \mathbf{b})$ |              |             |   |    |

|                                                  |              |             |   |    |

|                                                  |              |             |   |    |

|                                                  |              |             |   |    |

#### **EX-OR GATE (XOR):**

An XOR gate (sometimes referred to by its extended name, Exclusive OR gate) is a digital logic gate with two or more inputs and one output that performs exclusive disjunction. The output of an XOR gate is true only when exactly one of its inputs is true. If both of an XOR gate's inputs are false, or if both of its inputs are true, then the output of the XOR gate is false.

| EQUATION  | LOGIC SYMBOL         | TRUTH TABLE |   |   |

|-----------|----------------------|-------------|---|---|

|           |                      | A           | В | Y |

| Y = a ^ b | $\rightarrow \Gamma$ |             |   |   |

|           |                      |             |   |   |

|           | /                    |             |   |   |

|           |                      |             |   |   |

#### **EX-NOR GATE (XNOR):**

An XNOR gate (sometimes referred to by its extended name, Exclusive NOR gate) is a digital logic gate with two or more inputs and one output that performs logical equality. The output of an XNOR gate is true when all of its inputs are true or when all of its inputs are false. If some of its inputs are true and others are false, then the output of the XNOR gate is false.

| EQUATION               | LOGIC SYMBOL | TRUTH TABLE |   | LE |

|------------------------|--------------|-------------|---|----|

|                        |              | A           | В | Y  |

| $Y = \sim (a \land b)$ | -            |             |   |    |

| 1 ( <b>a</b> 2)        |              |             |   |    |

|                        | ,            |             |   |    |

|                        |              |             |   |    |

#### **BUFFER GATE:**

A buffer has only a single input and a single output with behavior that is the opposite of an NOT gate. It simply passes its input, unchanged, to its output. In a boolean logic simulator, a buffer is mainly used to increase propagation delay. In a real-world circuit, a buffer can be used to amplify a signal if its current is too weak.

| EQUATION | LOGIC SYMBOL | TRUTH | TABLE |

|----------|--------------|-------|-------|

| Y = A    | :>-          | A     | Y     |

|          |              |       |       |

#### **PROCEDURE:**

#### Software part

- 1. Click on the Xilinx ISE Design Suite 12.1or Xilinx Project navigator icon on the desktop of PC.

- 2. Write the Verilog code by choosing HDL as top level source module.

- 3. Check syntax, view RTL schematic and note the device utilization summary by double clicking on the synthesis in the process window.

- 4. Perform the functional simulation using Xilinx ISE simulator.

- 5. The output can be observed by using ISIM Simulator.

#### **PROGRAM:**

#### **BASIC GATES:**

| DATAFLOW               | BEHAVIORAL             | STRUCTURAL             |  |

|------------------------|------------------------|------------------------|--|

| NOT GATE               |                        |                        |  |

| module notgate(a,y);   | module notgate (a,y);  | module notgate (a,y)   |  |

| input a;               | input a;               | input a;               |  |

| output y;              | output y;              | output y;              |  |

| assign y= ∼a;          | reg y;                 | inv a1(y,a);           |  |

| endmodule              | always @(a)            | endmodule              |  |

|                        | begin                  |                        |  |

|                        | y=~a;                  |                        |  |

|                        | end                    |                        |  |

|                        | endmodule              |                        |  |

|                        | OR GATE                |                        |  |

| module orgate(a,b,y);  | module orgate(a,b,y);  | module orgate(a,b,y);  |  |

| inpput a,b;            | input a,b;             | input a,b;             |  |

| output y;              | output y;              | output y;              |  |

| assign $y=(a b)$ ;     | reg y;                 | or a1(y,a,b);          |  |

| endmodule              | always @(a,b)          | endmodule              |  |

|                        | begin                  |                        |  |

|                        | y=a b;                 |                        |  |

|                        | end                    |                        |  |

|                        | endmodule              |                        |  |

| AND GATE               |                        |                        |  |

| module andgate(a,b,y); | module andgate(a,b,y); | module andgate(a,b,y); |  |

| input a,b;             | input a,b;             | input a,b;             |  |

| output y;              | output y;              | output y;              |  |

| assign y=(a&b);        | reg y;                 | and a1(y,a,b);         |  |

| endmodule              | always @(a,b)          | endmodule              |  |

|                        | begin                  |                        |  |

|                        | y=a&b                  |                        |  |

|                        | end                    |                        |  |

|                        | endmodule              |                        |  |

|                        |                        |                        |  |

|                         | NOR GATE                |                         |

|-------------------------|-------------------------|-------------------------|

| module norgate(a,b,y);  | module norgate(a,b,y);  | module norgate(a,b,y);  |

| inpput a,b;             | input a,b;              | input a,b;              |

| output y;               | output y;               | output y;               |

| assign $y=\sim(a b)$ ;  | reg y;                  | nor a1(y,a,b);          |

| endmodule               | always @(a,b)           | endmodule               |

|                         | begin                   |                         |

|                         | $y=\sim(a b);$          |                         |

|                         | end                     |                         |

|                         | endmodule               |                         |

|                         | NAND Gate               |                         |

| module nandgate(a,b,y); | module nandgate(a,b,y); | module nandgate(a,b,y); |

| input a,b;              | input a,b;              | input a,b;              |

| output y;               | output y;               | output y;               |

| assign y=~(a&b);        | reg y;                  | nand a1(y,a,b);         |

| endmodule               | always @(a,b)           | endmodule               |

|                         | begin                   |                         |

|                         | y=~(a&b);               |                         |

|                         | end                     |                         |

|                         | endmodule               |                         |

|                         | XOR Gate                |                         |

| module xorgate(a,b,y);  | module xorgate(a,b,y);  | module xorgate(a,b,y);  |

| input a,b;              | input a,b;              | input a,b;              |

| output y;               | output y;               | output y;               |

| assign y=(a^b);         | reg y;                  | xor a1(y,a,b);          |

| endmodule               | always @(a,b)           | endmodule               |

|                         | begin                   |                         |

|                         | y=a^b;                  |                         |

|                         | end                     |                         |

|                         | endmodule               |                         |

|                         | XNOR GATE               |                         |

| module xnorgate(a,b,y); | module xnorgate(a,b,y); | module xnorgate(a,b,y); |

| input a,b;              | input a,b;              | input a,b;              |

| output y;               | output y;               | output y;               |

| assign $y=(\sim(a^b));$ | reg y;                  | xnor al(y,a,b);         |

| endmodule               | always @(a,b)           | endmodule               |

|                                        | begin                              |                                    |  |

|----------------------------------------|------------------------------------|------------------------------------|--|

|                                        | $y=\sim(a^b);$                     |                                    |  |

|                                        | end                                |                                    |  |

|                                        | endmodule                          |                                    |  |

|                                        |                                    |                                    |  |

|                                        | BUFFER GATE                        |                                    |  |

| module bufgate (a,y);                  | module bufgate (a,y);              | module bufgate (a,y);              |  |

| input a;                               | input a;                           | input a;                           |  |

| output y;                              | output y;                          | •                                  |  |

| assign y= a;                           | reg y;                             | output y;                          |  |

| endmodule                              | always @(a)                        | buf(y,a);                          |  |

|                                        | begin                              | endmodule                          |  |

|                                        | y=a;                               |                                    |  |

|                                        | end                                |                                    |  |

|                                        | endmodule                          |                                    |  |

| BASIC GATES (ALL GATES IN ONE PROGRAM) |                                    |                                    |  |

| module gates(a,b,c,d,e,f,g,h,i,j);     | module gates(a,b,c,d,e,f,g,h,i,j); | module gates(a,b,c,d,e,f,g,h,i,j); |  |

| input a,b;                             | input a,b;                         | input a,b;                         |  |

| output c,d,e,f,g,h,i,j;                | output c,d,e,f,g,h,i,j;            | output c,d,e,f,g,h,i,j;            |  |

| assign c=a&b                           | reg c,d,e,f,g,h,i,j;               | and (c,a,b);                       |  |

| assign d=a b;                          | always @(a,b)                      | or(d,a,b);                         |  |

| assign e=~a;                           | begin                              | not(e,a);                          |  |

| assign f=a;                            | c=a&b                              | buf(f,a);                          |  |

| assign $g=\sim(a b)$ ;                 | d=a b;                             | nor(g,a,b);                        |  |

| assign h=a^b;                          | e=~a;                              | xor(h,a,b);                        |  |

| assign $i=\sim(a^b);$                  | f=a;                               | xnor(i,a,b);                       |  |

| assign $j=\sim(a\&b)$ ;                | $g=\sim(a b);$                     | nand(j,a,b);                       |  |

| endmodule                              | h=a^b;                             | endmodule                          |  |

|                                        | i=~(a^b);                          |                                    |  |

|                                        | j=~(a&b);                          |                                    |  |

|                                        | end                                |                                    |  |

|                                        | endmodule                          |                                    |  |

| EXP.NO: | SIMULATION OF ADDER |

|---------|---------------------|

| DATE:   |                     |

To write a Verilog program for Adder and to synthesize, simulate it using Xilinx software tool.

.

#### **TOOLS REQUIRED:**

#### Software:

1. Xilinx ISE Design Suite 12.1

#### THEORY:

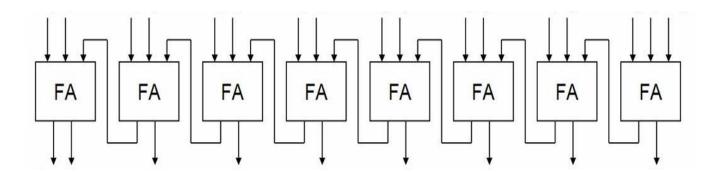

When you add large numbers carefully together the addition is done digit by digit. In the illustration, two 8 —digit binary numbers are being added. The top row contains the first number and the second row the other. Working from the right-hand side, there can be no 'carry' to add to the sum of the first two digits, so a half adder is sufficient. But for the second and subsequent pairs of digits, full adders must be use (any carry' is indicated by a f below the adder). The output will be an 8-bit and if the carry is formed that will be shown in cout output value.

#### **PROCEDURE:**

#### Software part

- 1. Click on the Xilinx ISE Design Suite 12.1or Xilinx Project navigator icon on the desktop of PC.

- 2. Write the Verilog code by choosing HDL as top level source module.

- 3. Check syntax, view RTL schematic and note the device utilization summary by double

- 4. Clicking on the synthesis in the process window.

- 5. Perform the functional simulation using Xilinx ISE simulator.

- 6. The output can be observed by using ISIM Simulator.

#### **PROGRAM:**

#### **8-BIT RIPPLE CARRY ADDER:**

```

module half_adder(a,b,sum,carry);

input a,b;

output sum, carry;

xor(sum,a,b);

and(carry,a,b);

endmodule

module full_adder(a,b,c,sum,carry);

input a,b,c;

output sum, carry;

wire w1, w2, w3;

half_adder hal(a,b,w1,w2);

half_adder ha2(c,w1,sum,w3);

or(carry,w2,w3);

endmodule

module rippleadder(a, b, cin, sum, cout);

input [7:0] a,b;

input cin;

output [7:0]sum;

output cout;

wire[6:0] c;

full_adder a1(a[0],b[0],cin,sum[0],c[0]);

full_adder a2(a[1],b[1],c[0],sum[1],c[1]);

full_adder a3(a[2],b[2],c[1],sum[2],c[2]);

full_adder a4(a[3],b[3],c[2],sum[3],c[3]);

full adder a5(a[4],b[4],c[3],sum[4],c[4]);

full_adder a6(a[5],b[5],c[4],sum[5],c[5]);

full_adder a7(a[6],b[6],c[5],sum[6],c[6]);

full_adder a8(a[7],b[7],c[6],sum[7],cout);

endmodule

```

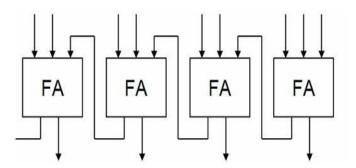

#### 4-BIT RIPPLE CARRY ADDER

```

module half_adder(a,b,sum,carry);

input a,b;

output sum, carry;

xor(sum,a,b);

and(carry,a,b);

endmodule

module full_adder(a,b,c,sum,carry);

input a,b,c;

output sum, carry;

wire w1, w2, w3;

half_adder ha1(a,b,w1,w2);

half_adder ha2(c,w1,sum,w3);

or(carry,w2,w3);

endmodule

module rippleadder (a, b, cin, sum, cout);

input [3:0]a,b;

input cin;

output [3:0]sum;

output cout;

wire[2:0] c;

full_adder a1(a[0],b[0],cin,sum[0],c[0]);

full_adder a2(a[1],b[1],c[0],sum[1],c[1]);

full_adder a3(a[2],b[2],c[1],sum[2],c[2]);

full_adder a4(a[3],b[3],c[2],sum[3],cout);

endmodule

```

| SIMULATION REPORT: |  |  |

|--------------------|--|--|

|                    |  |  |

|                    |  |  |

|                    |  |  |

|                    |  |  |

|                    |  |  |

|                    |  |  |

|                    |  |  |

|                    |  |  |

|                    |  |  |

| RESULT:            |  |  |

|                    |  |  |

| EXP.NO: | SIMULATION OF MULTIPLIER |

|---------|--------------------------|

| DATE:   |                          |

To write a Verilog program for 4-bit multiplier and to synthesize, simulate it using Xilinx software tool.

#### **TOOLS REQUIRED:**

#### SOFTWARE:

1. Xilinx ISE Design Suite 12.1

#### THEORY:

Multiplication of two elements in the polynomial basis can be accomplished in the normal way of multiplication, but there are a number of ways to speed up multiplication, especially in hardware. In this type the multiplication can done parallel counter and it is generate carry. The multiplication is independent of the carry so we can perform N number of multiplication independent of carry.

#### **PROCEDURE:**

#### Software part

- 1. Click on the Xilinx ISE Design Suite 12.1or Xilinx Project navigator icon on the desktop of PC.

- 2. Write the Verilog code by choosing HDL as top level source module.

- 3. Check syntax, view RTL schematic and note the device utilization summary by double

- 4. Clicking on the synthesis in the process window.

- 5. Perform the functional simulation using Xilinx ISE simulator.

- 6. The output can be observed by using ISIM Simulator.

#### **PROGRAM:**

#### **4-BIT ARRAY MULTIPLIER:**

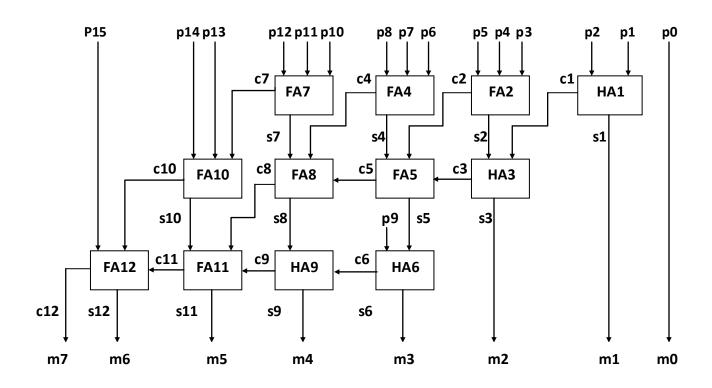

a0b0=p0 a0b1=p2 a0b2=p5 a0b3=p9 a1b0=p1 a1b1=p4 a1b2=p8 a1b3=p12 a2b0=p3 a2b1=p7 a2b2=p11 a2b3=p14 a3b0=p6 a3b1=p10 a3b2=p13 a3b3=p15

### **PROGRAM:**

```

module half_adder(a,b,sum,carry);

input a,b;

output sum, carry;

xor(sum,a,b);

and(carry,a,b);

endmodule

module full_adder(a,b,c,sum,carry);

input a,b,c;

output sum, carry;

wire w1, w2, w3;

half_adder ha1(a,b,w1,w2);

half_adder ha2(c,w1,sum,w3);

or(carry,w2,w3);

endmodule

module arraymultiplier(m,a,b);

input [3:0]a,b;

output [7:0]m;

wire [15:0]p;

wire [12:1]s,c;

and (p[0], a[0], b[0]);

and(p[1],a[1],b[0]);

and(p[2],a[0],b[1]);

and(p[3],a[2],b[0]);

and(p[4],a[1],b[1]);

and(p[5],a[0],b[2]);

and(p[6],a[3],b[0]);

and(p[7],a[2],b[1]);

and (p[8], a[1], b[2]);

and(p[9],a[0],b[3]);

and(p[10],a[3],b[1]);

and(p[11],a[2],b[2]);

```

```

and(p[12],a[1],b[3]);

and(p[13],a[3],b[2]);

and (p[14], a[2], b[3]);

and(p[15],a[3],b[3]);

half_adder ha1(s[1],c[1],p[1],p[2]);

full_adder fa2(s[2],c[2],p[4],p[3],p[5]);

half_adder ha3(s[3],c[3],s[2],c[1]);

full_adder fa4(s[4],c[4],p[6],p[7],p[8]);

full_adder fa5(s[5],c[5],s[4],c[2],c[3]);

half_adder ha6(s[6],c[6],s[5],p[9]);

full_adder fa7(s[7],c[7],p[10],p[11],p[12]);

full_adder fa8(s[8],c[8],c[5],c[4],s[7]);

half_adder ha9(s[9],c[9],s[8],c[6]);

full_adder fa10(s[10],c[10],p[14],p[13],c[7]);

full_adder fa11(s[11],c[11],c[9],c[8],s[10]);

full\_adder\ fa12(s[12],c[12],p[15],c[10],c[11]);

buf(m[0],p[0]);

buf(m[1],s[1]);

buf(m[2],s[3]);

buf(m[3],s[6]);

buf(m[4],s[9]);

buf(m[5],s[11]);

buf(m[6],s[12]);

buf(m[7],c[12]);

endmodule

4-BIT MULTIPLIER

```

```

module adder(a,b, out);

input [3:0]a,b;

output [7:0]out;

assign out= a*b;

endmodule

```

| SIMULATION REPORT: |

|--------------------|

|                    |

|                    |

|                    |

|                    |

|                    |

|                    |

|                    |

|                    |

|                    |

|                    |

| RESULT:            |

|                    |

|                    |

| EXP.NO: | SIMULATION OF 8-BIT ARITHMETIC AND LOGIC UNIT |

|---------|-----------------------------------------------|

| DATE:   |                                               |

To write a Verilog program for 8-bit Arithmetic and Logic Unit and to synthesize, simulate it using Xilinx software tool.

#### **TOOLS REQUIRED:**

#### **SOFTWARE:**

1. Xilinx ISE Design Suite 12.1

#### THEORY:

#### 8-BIT ARITHMETIC AND LOGIC UNIT:

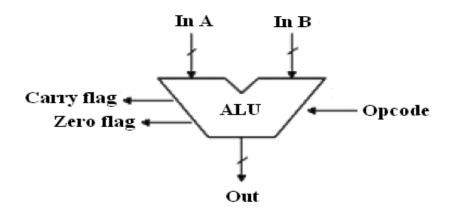

ALU is the fundamental building block of the processor, which is responsible for carrying out the arithmetic and logic functions. ALU comprises of combinatorial logic that implements arithmetic operations such as Addition, Subtraction and Multiplication, and logic operations such as AND, OR, NOT. The ALU gets operands from the register file or memory.

The block diagram of a typical ALU is shown in Figure below. The ALU reads two input operands In A and In B. The operation to perform on these input operands is selected using the control input Opcode. The ALU performs the selected operation on the input operands In A and In B and produces the output, Out. The ALU also updates different flag signals after performing the selected function. Note that the ALU is purely combinatorial logic and contains no registers or latches.

The **arithmetic functions** are much more complex to implement than the **logic functions**. The performance of the **ALU** depends upon the architecture of each structural components of the **ALU**. In this example only some basic **ALU** functions are implemented. The **ALU** is divided into an arithmetic section and a logical section.

The **Arithmetic Unit** compromises of three functions. They are:

- Addition

- o Subtraction

- Multiplication

The **Logical Unit** compromises of five functions. They are:

- Bitwise AND

- Bitwise OR

- o Bitwise NAND

- o Bitwise NOR

- Bitwise XOR

Flags: **ALU** updates the **conditional flags**, which are used by the processor to perform other operations like condition checking and branching. In this example two flags are implemented. They are:

**Zero** - If all the bits of the result data are zero then the zero flag is set

o Carry out - If the addition of the two operands gives the carry out this flag is set

#### 2. Truth Table

The Figure below shows the truth table of the **8-bit ALU**. The **ALU** works on **8-bit operands**. It supports **8 instructions** which are selected by the **3-bit Opcode**.

| S.No. | Opcode | Operation                       |

|-------|--------|---------------------------------|

| 1     | 000    | Result = Operand1 + Operand2    |

| 2     | 001    | Result = Operand1 - Operand2    |

| 3     | 010    | Result = Operand1 * Operand2    |

| 4     | 011    | Result = Operand1 & Operand2    |

| 5     | 100    | Result = Operand1   Operand2    |

| 6     | 101    | Result = ~(Operand1 & Operand2) |

| 7     | 110    | Result = ~(Operand1   Operand2) |

| 8     | 111    | Result = Operand1 ^ Operand2    |

Truth table for 8-bit ALU.

### **PROCEDURE:**

### **Software part:**

- 1. Click on the Xilinx ISE Design Suite 12.1or Xilinx Project navigator icon on the desktop of PC.

- 2. Write the Verilog code by choosing HDL as top level source module.

- 3. Check syntax, view RTL schematic and note the device utilization summary by double clicking on the synthesis in the process window.

- 4. Perform the functional simulation using Xilinx ISE simulator.

- **5.** The output can be observed by using ISIM Simulator

### Verilog Module:

```

module ALU1 (

input [7:0] A,B, // ALU 8-bit Inputs

input [3:0] ALU_Sel,// ALU Selection

output [7:0] ALU_Out, // ALU 8-bit Output

output CarryOut // Carry Out Flag

);

reg [7:0] ALU_Result;

wire [8:0] tmp;

assign ALU_Out = ALU_Result; // ALU out

assign tmp = {1'b0,A} + {1'b0,B};

assign CarryOut = tmp[8]; // Carryout flag

```

```

always @(*)

begin

case(ALU_Sel)

4'b0000: // Addition

ALU Result = A + B;

4'b0001: // Subtraction

ALU_Result = A - B;

4'b0010: // Multiplication

ALU_Result = A * B;

4'b0100: // Logical shift left

ALU_Result = A << 1;

4'b0101: // Logical shift right

ALU_Result = A >> 1;

4'b0110: // Rotate left

ALU_Result = \{A[6:0], A[7]\};

4'b0111: // Rotate right

ALU_Result = \{A[0], A[7:1]\};

4'b1000: // Logical and

ALU_Result = A \& B;

4'b1001: // Logical or

ALU_Result = A \mid B;

4'b1010: // Logical xor

ALU_Result = A ^ B;

4'b1011: // Logical nor

ALU_Result = \sim (A \mid B);

4'b1100: // Logical nand

ALU_Result = \sim (A \& B);

4'b1101: // Logical xnor

ALU_Result = \sim (A \land B);

4'b1110: // Greater comparison

ALU_Result = (A>B)?8'd1:8'd0;

4'b1111: // Equal comparison

ALU_Result = (A==B)?8'd1:8'd0;

default: ALU_Result = A + B;

```

| endcase            |  |  |

|--------------------|--|--|

| end                |  |  |

| endmodule          |  |  |

|                    |  |  |

| SIMULATION REPORT: |  |  |

|                    |  |  |

|                    |  |  |

|                    |  |  |

|                    |  |  |

|                    |  |  |

|                    |  |  |

|                    |  |  |

|                    |  |  |

|                    |  |  |

|                    |  |  |

|                    |  |  |

|                    |  |  |

|                    |  |  |

|                    |  |  |

|                    |  |  |

|                    |  |  |

|                    |  |  |

|                    |  |  |

|                    |  |  |

|                    |  |  |

|                    |  |  |

|                    |  |  |

|                    |  |  |

|                    |  |  |

|                    |  |  |

|                    |  |  |

|                    |  |  |

| RESULT:            |  |  |

|                    |  |  |

|                    |  |  |

|                    |  |  |

| EXP.NO: | SIMULATION OF UNIVERSAL SHIFT REGISTER |

|---------|----------------------------------------|

| DATE:   |                                        |

### AIM:

To write a verilog program for Universal Shift Register and to synthesize, simulate it using Xilinx software tool.

### **TOOLS REQUIRED:**

Software:

1. Xilinx ISE Design Suite 12.1

### THEORY:

#### **UNIVERSAL SHIFT REGISTER:**

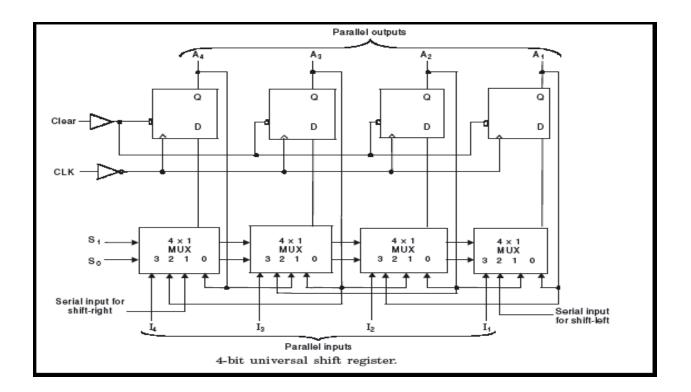

A Unidirectional shift register is a register that can capable of transferring data in only one direction. Whereas the register that is capable of transferring data in both left and right direction is called a 'bidirectional shift register.' Now let we have a register which can capable to transfer data in both the shift-right and shift-left, along with the necessary input and output terminals for parallel transfer, then it is called a *shift register* with *parallel load* or 'universal shift register.'

A shift-right control to enable the shift-right operation and the serial input and output lines associated with the shift-right.

A shift-left control to enable the shift-left operation and the serial input and output lines associated with the shift-left.

A parallel-load control to enable a parallel transfer and the n input lines associated with the parallel transfer.

*n* parallel output lines.

A *clear* control to clear the register to 0.

A *CLK* input for clock pulses to synchronize all operations.

A control state that leaves the information in the register unchanged even though clock pulses are continuously applied.

### **PROCEDURE:**

### Software part

- 1. Click on the Xilinx ISE Design Suite 12.1or Xilinx Project navigator icon on the desktop of PC.

- 2. Write the Verilog code by choosing HDL as top level source module.

- 3. Check syntax, view RTL schematic and note the device utilization summary by double Clicking on the synthesis in the process window.

- 4. Perform the functional simulation using Xilinx ISE simulator.

- 5. The output can be observed by using ISIM Simulator.

### **PROGRAM:**

| S1 | S0 | REGISTER<br>OPERATION |

|----|----|-----------------------|

| 0  | 0  | No changes            |

| 0  | 1  | Shift right           |

| 1  | 0  | Shift left            |

| 1  | 1  | Parallel load         |

module universal shift(a,s,clk,p); input [3:0]a; input [1:0]s; input clk; output reg [3:0]p; initial p<=4'b0110; always@(posedge clk) begin case (s) 2'b00: begin p[3] <= p[3];p[2] <= p[2];p[1]<=p[1]; p[0] < = p[0];end 2'b01: begin p[3]<=p[0]; p[2] <= p[3];p[1] <= p[2];

end

p[0]<=p[1];

```

2'b10:

begin

p[0]<=p[3];

p[1]<=p[0];

p[2]<=p[1];

p[3]<=p[2];

end

2'b11:

begin

p[0] <= a[0];

p[1] <= a[1];

p[2] <= a[2];

p[3]<=a[3];

end

endcase

end

endmodule

```

## **SIMULATION REPORT:**

# EXP.NO: DATE: SIMULATION AND DESIGN OF MEMORIES

### AIM:

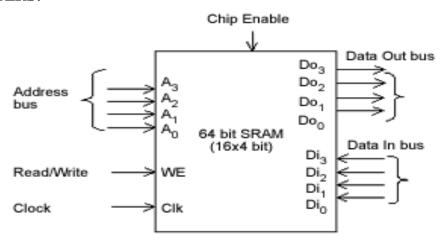

To write a Verilog program for a 16x4 memory and to synthesize, simulate it using Xilinx software tool.

### **TOOLS REQUIRED:**

Software:

1. Xilinx ISE Design Suite 12.1

### THEORY:

### **MOD 10 COUNTERS:**

The memory block diagram is shown in above figure. It takes a few assumptions into consideration for easing the operations of the circuit. While data input pin and address pin may have any value depending on the specifications of memory used and your need, clock used in the circuit is active high.

Enable pin triggers the circuit when it is active high, and read operation is performed when read/write pin is high, while write operation is performed when read/write pin is active low.

### **PROCEDURE:**

### Software part

- 1. Click on the Xilinx ISE Design Suite 12.1or Xilinx Project navigator icon on the desktop of PC.

- 2. Write the Verilog code by choosing HDL as top level source module.

- 3. Check syntax, view RTL schematic and note the device utilization summary by double clicking on the synthesis in the process window.

- 4. Perform the functional simulation using Xilinx ISE simulator.

- 5. The output can be observed by using ISIM Simulator.

### **PROGRAM:**

```

module memory_16x4(op,ip,rd_wr,clk,address);

output reg [3:0] op;

input [3:0] ip;

input [3:0] address;

input rd_wr,clk;

reg [3:0] memory[0:15];

always @ (posedge clk)

begin

if (rd_wr)

op=memory[address];

else

begin

memory[address]=ip;

end

end

endmodule // memory_16x4

```

| Sr. No. | Name of the Pin | Direction | Width | Description             |

|---------|-----------------|-----------|-------|-------------------------|

| 1       | Address         | Input     | 4     | Input address           |

| 2       | Ip              | input     | 4     | Input data to memory    |

| 3       | Rd_wr           | Input     | 1     | Control signal          |

|         |                 |           |       | 1=read from memory      |

|         |                 |           |       | 0=write in to memory    |

| 4       | Clk             | Input     | 1     | Clock input             |

| 5       | op              | Output    | 4     | Output read from memory |

| EXP.NO: | ANALYSIS AND SIMULATION OF STATE MACHINES |

|---------|-------------------------------------------|

| DATE:   |                                           |

### AIM:

To analyze, synthesize and simulate state machines using Xilinx simulation tool

### **TOOLS REQUIRED:**

Software:

1. Xilinx ISE Design Suite 12.1

### THEORY:

### **MEALY MODEL:**

Analysis describes what a given circuit will do under certain operating conditions. The behavior of a clocked sequential circuit is determined from the inputs, the outputs, and the state of its flip-flops. The outputs and the next state are both a function of the inputs and the present state. The analysis of a sequential circuit consists of obtaining a table or a diagram for the time sequence of inputs, outputs, and internal states. It is also possible to write Boolean expressions that describe the behavior of the sequential circuit. These expressions must include the necessary time sequence, either directly or indirectly. A logic diagram is recognized as a clocked sequential circuit if it includes flip-flops with clock inputs. The flip-flops may be of any type, and the logic diagram may or may not include combinational logic gates.

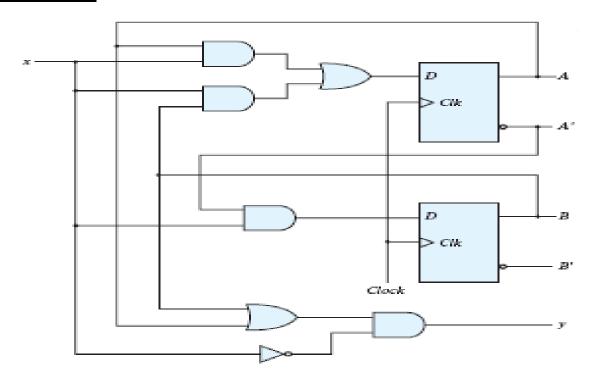

State Equations: The behavior of a clocked sequential circuit can be described algebraically by means of state equations. A *state equation* (also called a *transition equation*) specifies the next state as a function of the present state and inputs. Consider the sequential circuit shown in Fig. 1. It acts as a 0-detector by asserting its output when a 0 is detected in a stream of 1s.

$$A(t+1) = A(t)x(t) + B(t)x(t)$$

;  $B(t+1) = A'(t)x(t)$ ;  $y(t) = [A(t) + B(t)]x'(t)$

A state equation is an algebraic expression that specifies the condition for a flip-flop state transition. The left side of the equation, with (t + 1), denotes the next state of the flip-flop one clock edge later. The right side of the equation is a Boolean expression that specifies the present state and input conditions that make the next state equal to 1. Since all the variables in the Boolean expressions are a function of the present state, we can omit the designation (t) after each variable for convenience and can express the state equations in the more compact form

$$A(t+1) = Ax + Bx$$

;  $B(t+1) = A'x$ ;  $y = Ax' + Bx'$

### **LOGIC DIAGRAM:**

### **STATE TABLE:**

The time sequence of inputs, outputs, and flip-flop states can be enumerated in a *state table* (sometimes called a *transition table*). The table consists of four sections labeled *present state*, *input*, *next state*, and *output*. The present-state section shows the states of flip-flops A and B at any given time t. The input section gives a value of x for each possible present state. The next-state section shows the states of the flip-flops one clock cycle later, at time t+1. The output section gives the value of y at time t for each present state and input condition. State table for the above Circuit diagram

|   | Present<br>State |   | Next | State | Output |

|---|------------------|---|------|-------|--------|

| A | В                | X | A    | В     | y      |

| 0 | 0                | 0 | 0    | 0     | 0      |

| 0 | 0                | 1 | 0    | 1     | 0      |

| 0 | 1                | 0 | 0    | 0     | 1      |

| 0 | 1                | 1 | 1    | 1     | 0      |

| 1 | 0                | 0 | 0    | 0     | 1      |

| 1 | 0                | 1 | 1    | 0     | 0      |

| 1 | 1                | 0 | 0    | 0     | 1      |

| 1 | 1                | 1 | 1    | 0     | 0      |

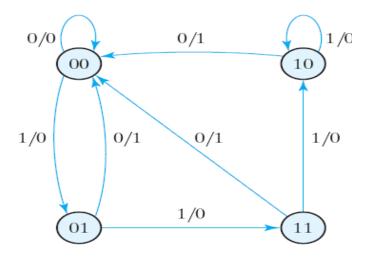

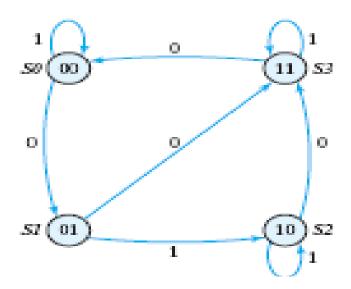

### **STATE DIAGRAM:**

The information available in a state table can be represented graphically in the form of a state diagram. In this type of diagram, a state is represented by a circle, and the (clock-triggered) transitions between states are indicated by directed lines connecting the circles. The state diagram provides the same information as the state table and is obtained directly from Table. The binary number inside each circle identifies the state of the flip-flops. The directed lines are labeled with two binary numbers separated by a slash. The input value during the present state is labeled first, and the number after the slash gives the output during the present state with the given input. A directed line connecting a circle with itself indicates that no change of state occurs.

### **PROGRAM:**

### **MEALY MODEL:**

```

module Mealy_model(y, x, clk, reset);

input x,clk,reset;

output reg y;

reg [1:0] state, next_state;

parameter S0 = 2'b00, S1 = 2'b01, S2 = 2'b10, S3 = 2'b11;

always @ (posedge clk)

if (reset == 0) state <= S0;

else state <= next_state;

always @ (state, x)

case (state)

S0: if (x) next_state = S1; else next_state = S0;

```

S1: if (x) next\_state = S3; else next\_state = S0;

S2: if (x) next\_state = S2; else next\_state = S0;

S3: if (x) next\_state = S2; else next\_state = S0;

endcase

always @ (state, x)

case (state)

S0: y = 0;

S1, S2, S3: y = ~x;

endcase

endmodule

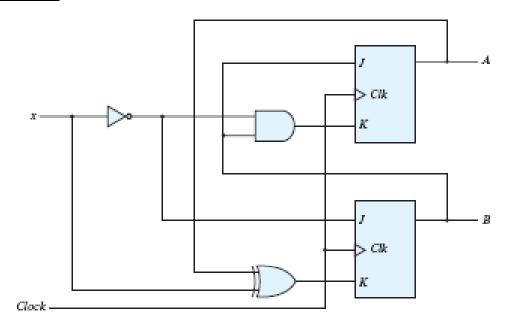

# MOORE MODEL: LOGIC DIAGRAM:

### **STATE TABLE:**

The time sequence of inputs, outputs, and flip-flop states can be enumerated in a *state table* (sometimes called a *transition table*). The table consists of four sections labeled *present state*, *input*, *next state*, and *output*. The present-state section shows the states of flip-flops A and B at any given time t. The input section gives a value of x for each possible present state. The next-state section shows the states of the flip-flops one clock cycle later, at time t+1. The output section gives the value of y at time t for each present state and input condition.

| Present State |   | Input | Next State |   | Flip- Flop Inputs |                |         |                |

|---------------|---|-------|------------|---|-------------------|----------------|---------|----------------|

| A             | В | X     | A          | В | $J_A$             | K <sub>A</sub> | $J_{B}$ | K <sub>B</sub> |

| 0             | 0 | 0     | 0          | 1 | 0                 | 0              | 1       | 0              |

| 0             | 0 | 1     | 0          | 0 | 0                 | 0              | 0       | 1              |

| 0             | 1 | 0     | 1          | 1 | 1                 | 1              | 1       | 0              |

| 0             | 1 | 1     | 1          | 0 | 1                 | 0              | 0       | 1              |

| 1             | 0 | 0     | 1          | 1 | 0                 | 0              | 1       | 1              |

| 1             | 0 | 1     | 1          | 0 | 0                 | 0              | 0       | 0              |

| 1 | 1 | 0 | 0 | 0 | 1 | 1 | 1 | 1 |

|---|---|---|---|---|---|---|---|---|

| 1 | 1 | 1 | 1 | 1 | 1 | 0 | 0 | 0 |

### **STATE EQUATIONS:**

$$A(t+1) = JA' + K'A$$

$$B(t+1) = JB' + K'B$$

$$A(t+1) = BA' + (Bx')'A = A'B+AB'+Ax$$

$$B(t+1) = x'B' + (A \oplus x)'B = B'x' + ABx + A'Bx'$$

### **STATE DIAGRAM:**

### **MOORE MODEL:**

module Moore\_Model(y, x, clk, reset);

input x,clk,reset;

output [1:0]y;

reg [1:0] state;

parameter S0 = 2'b00, S1 = 2'b01, S2 = 2'b10, S3 = 2'b11;

always @ (posedge clk)

if (reset == 0) state  $\leq S0$ ;

else case (state)

S0: if (x) state  $\leq$  S0; else state  $\leq$  S1;

S1: if (x) state  $\leq$  S2; else state  $\leq$  S3;

S2: if (x) state  $\leq$  S2; else state  $\leq$  S3;

| S3: if (x) state <= S3; else st<br>endcase | , |  |  |

|--------------------------------------------|---|--|--|

| assign y=state;                            |   |  |  |

| endmodule                                  |   |  |  |

|                                            |   |  |  |

|                                            |   |  |  |

|                                            |   |  |  |

|                                            |   |  |  |

|                                            |   |  |  |

|                                            |   |  |  |

|                                            |   |  |  |

|                                            |   |  |  |

|                                            |   |  |  |

|                                            |   |  |  |

|                                            |   |  |  |

|                                            |   |  |  |

|                                            |   |  |  |

|                                            |   |  |  |

|                                            |   |  |  |

|                                            |   |  |  |

|                                            |   |  |  |

|                                            |   |  |  |

|                                            |   |  |  |

|                                            |   |  |  |

|                                            |   |  |  |

|                                            |   |  |  |

|                                            |   |  |  |

|                                            |   |  |  |

|                                            |   |  |  |

|                                            |   |  |  |

|                                            |   |  |  |

|                                            |   |  |  |

# TANNER

TOOLS

# **Introduction to Tanner Tool**

Tanner tool is a Spice Computer Analysis Programmed for Analogue Integrated Circuits. Tanner tool consists of the following Engine Machines:

- 1. S-EDIT (Schematic Edit)

- 2. T-EDIT (Simulation Edit)

- 3. W-EDIT (Waveforms Edit)

- 4. L-EDIT (Layout Edit)

Using these engine tools, spice program provides facility to the use to design & simulate new ideas in Analogue Integrated Circuits before going to the time consuming & costly process of chip fabrication.

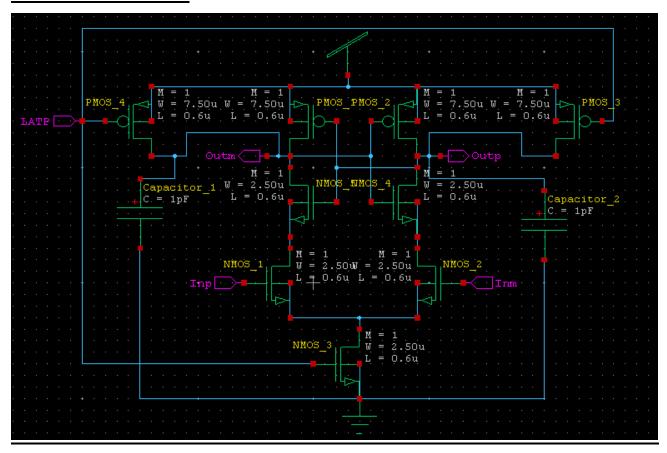

### > SCHEMATIC EDIT TOOL (S-EDIT)

S-Edit is hierarchy of files, modules & pages. It introduces symbol & schematic modes. S-Edit provides the facility of:

- 1. Beginning a design.

- 2. Viewing, drawing & editing of objects.

- 3. Design connectivity.

- 4. Properties, net lists & simulation.

- 5. Instance & browse schematic & symbol mode.

Beginning a design: It explains the design process in detail in terms of file module operation and module.

Browser: Effective schematic design requires a working knowledge of the S-Edit design hierarchy of files & modules. S-Edit design files consist of modules. A module is a functional unit of design such as a transistor, a gate and an amplifier.

Modules contain two components:

- 1) Primitives: Geometrical objects created with drawing tools.

- 2) Instances: References to other modules in file. The instanced module is the original.

- S-Edit has two viewing modes:

- 1. Schematic Mode: to create or view a schematic, we operate in schematic mode.

- 2. Symbol Mode: it represents symbol of a larger functional unit such as operational amplifier.

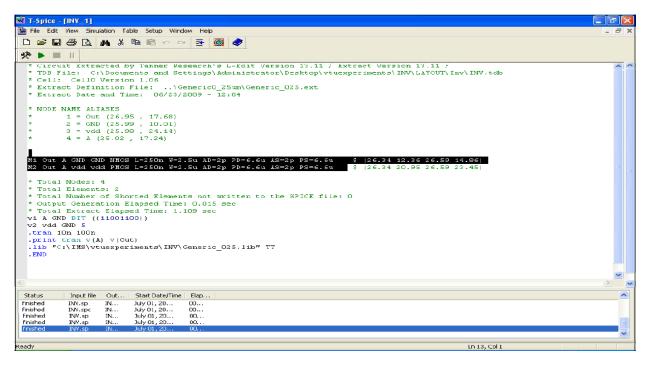

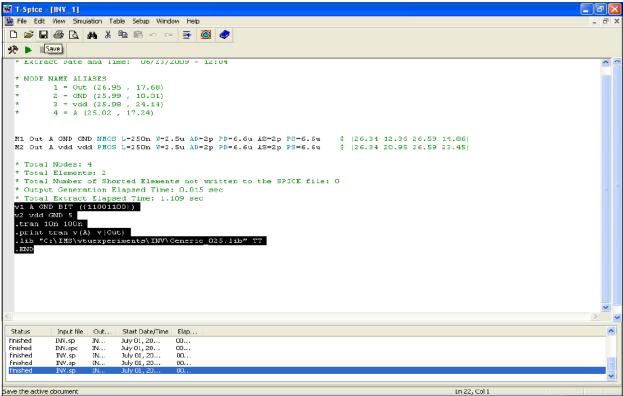

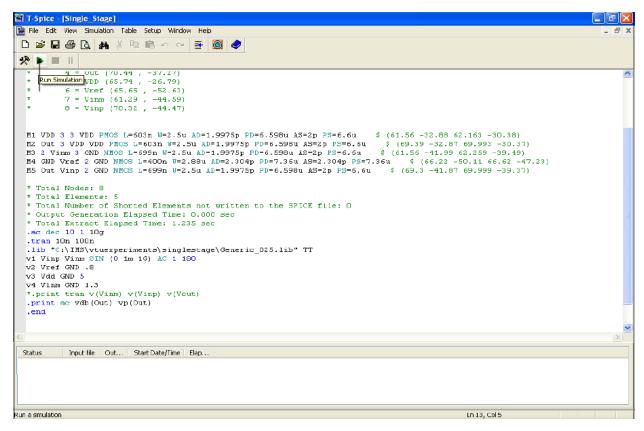

### T-SPICE PRO CIRCUIT ANALYSIS

An introduction to the integrated components of the T- Spice Pro circuit analysis suite:

Schematic data files (.sdb): describes the circuits to be analyzed in graphical form, for display and editing by S- Edit" Schematic Editor.

Simulation input files (.sp): describes the circuits to be analyzed in textual form, for editing and simulation by T- Spice" Circuit Simulator.

Simulation output files (.out): containing the numerical results of the circuit analyses, for manipulation and display by W- Edit" Waveform Viewer.

### **► CIRCUIT SIMULATOR (T-SPICE)**

T- Spice Pro's waveform probing feature integrates S- Edit, T- Spice, and W- Edit to allow individual points in a circuit to be specified and analyzed. A few analysis is described below:

The heart of T-Spice operation is the input file (also known as the circuit description, the net list & the input deck). This is a plain text file that contains the device statement & simulation commands, drawn from the SPICE circuit description language with which T-Spice constructs a model of the circuit to be simulated. Input files can be created and modified with any text editor.

T-Spice is a tool used for simulation of the circuit. It provides the facility of

- 1. Design Simulation

- 2. Simulation Commands

- 3. Device Statements

- 4. User-Designed External Models

- 5. Small Signal & Noise Models

T-Spice uses Kirchhoff's Current Law (KCL) to solve circuit problems. To T-Spice, a circuit is a set of devices attached to nodes. The voltage at all nodes represents the circuit state. T-Spice solves for a set of node voltage that satisfied KCL (implying that sum of currents flowing into each node is zero). In order to evaluate whether a set of node voltages is a solution, T-Spice computers and sums all the current flowing out of each device into nodes connected to it (its terminals). The relationship between the voltages at device terminals and the currents through the terminal is determined by the device model for a resistor of resistance R is

### $I=\Delta V/R$

Where,  $\Delta V$  represents the voltage difference across the device. A few analyses are discussed below:

### DC Operating Point Analysis

DC operating point analysis finds a circuit's steady- state condition, obtained (in principle) after the input voltages have been applied for an infinite amount of time. The .include command causes T- Spice to read in the contents of the model file for the evaluation of NMOS and PMOS transistors.

The technology file assigns values to MOSFET model parameters for both n - and p -type devices. When read by the input file, these parameters are used to evaluate MOSFET model equations, and the results are used to construct internal tables of current and charge values. Values read or interpolated from these tables are used in the computations called for by the simulation. Following each transistor name are the names of its terminals. The required order of terminal names is: drain -gate -source -bulk. Then the model name (NMOS or PMOS in this example), and physical characteristics such as length and width, are specified. The .op command performs a DC operating point calculation and writes the results to the file specified in the Simulate > Start Simulation dialog. The output file lists the DC operating point information for the circuit described by the input file.

### DC Transfer Analysis

DC transfer analysis is used to study the voltage or current at one set of points in a circuit as a function of the voltage or current at another set of points. This is done by sweeping the source variables over specified ranges, and recording the output. A list of sources to be swept, and the voltage ranges across which the sweeps are to take place follow the .dc command, indicating transfer analysis. The transfer analysis will be performed as follows: vdd will be set at 5 volts and vin will be swept over its specified range; vdd will then be incremented and vin will be reswept over its range; and so on, until vdd reaches the upper limit of its range. The .dc command ignores the values assigned to the voltage sources vdd and vin in the voltage source statements, but they must still be declared in those statements. The results for nodes in and out are reported by the .print dc command to the specified destination.

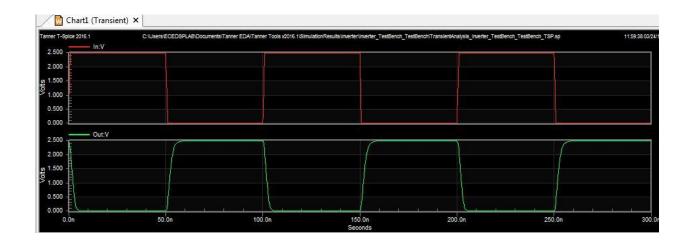

### **Transient Analysis**

Transient analysis provides information on how circuit elements vary with time. The basic T- Spice command for transient analysis has three modes. In the default mode, the DC operating point is computed, and T- Spice uses this as the starting point for the transient simulation. The .tran command specifies the characteristics of the transient analysis to be performed.

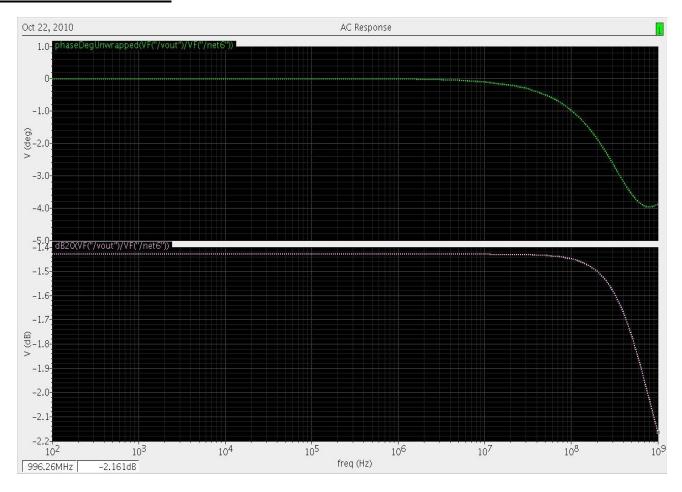

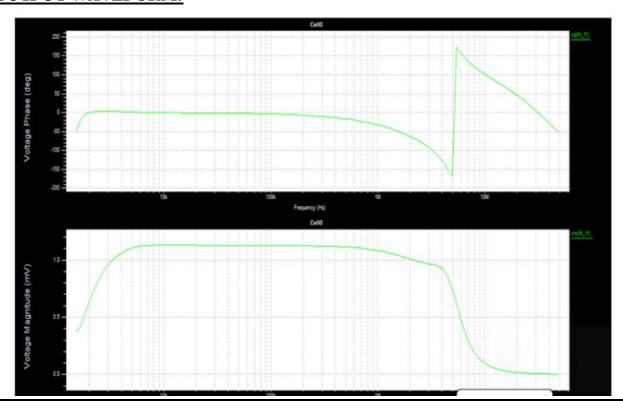

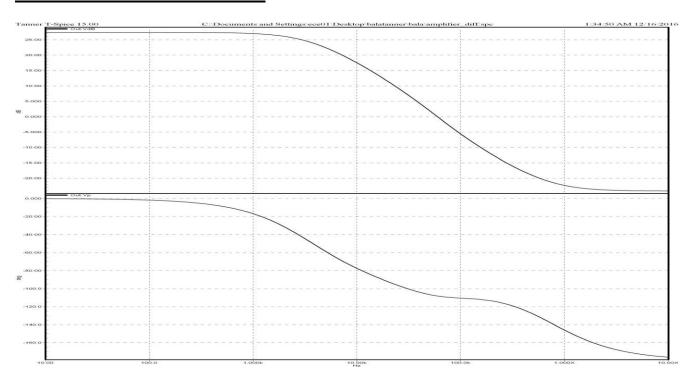

### **AC Analysis**

three steps: (1) calculating the DC operating point; (2) linearizing the circuit; and (3) solving the linearized circuit for each frequency. When ac voltage source is to be applied, then vdiff sets the DC voltage difference between nodes the two nodes to -0.0007 volts; its AC magnitude is 1 volt and its AC phase is 180 degrees. The .ac command performs an AC analysis. Following the .ac keyword is information concerning the frequencies to be swept during the analysis. In case, the frequency is to be swept logarithmically, by decades (DEC); 5 data points are to be included per decade is considered to be the standard The two .print commands write the voltage magnitude (in decibels) and phase (in degrees), respectively, for the node out to the specified file. The .acmodel command writes the small- signal model parameters and operating point voltages and currents for all circuit devices

### **Noise Analysis**

Real circuits, of course, are never immune from small, random fluctuations in voltage and current levels. In T- Spice, the influence of noise in a circuit can be simulated and reported in conjunction with AC analysis. The purpose of noise analysis is to compute the effect of the noise associated with various circuit devices on an output voltage or voltages as a function of frequency. Noise analysis is performed in conjunction with AC analysis; if the .ac command is missing, then the .noise command is ignored. With the .ac command present, the .noise command causes noise analysis to be performed at the same frequencies. The .noise command takes two arguments: the output at which the effects of noise are to be computed, and the input at which the .noise can be considered to be concentrated for the purposes of estimating the equivalent noise spectral density. The print command is used to print results.

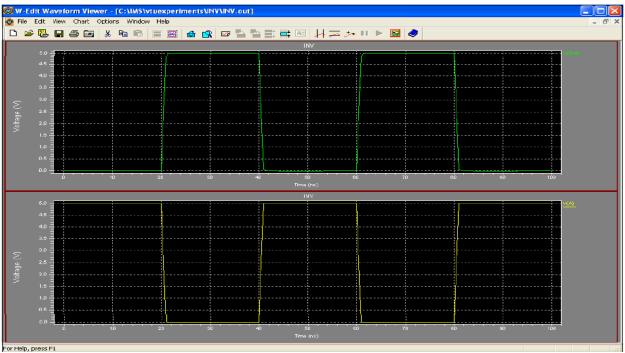

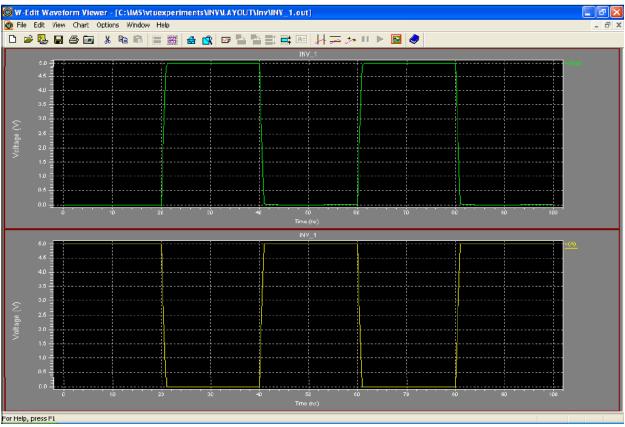

### > WAVEFORM EDIT

The ability to visualize the complex numerical data resulting from VLSI circuit simulation is critical to testing, understanding & improving these circuits. W-Edit is a waveform viewer that provides ease of use, power & speed in a flexible environment designed for graphical data representation. The advantages of W-Edit include:

- 1. Tight Integration with T-spice, Tanner EDA\_s circuit level simulator. W-Edit can chart data generated by T-spice directly, without modification of the output text data files. The data can also be charted dynamically as it is produced during the simulation.

- 2. Charts can automatically configure for the type of data being presented.

- 3. A data is treated by W-Edit as a unit called a trace. Multiple traces from different output files can be viewed simultaneously in single or several windows; traces can be copied and moved between charts & windows. Trace arithmetic can be performed on existed tracing to create new ones.

- 4. Chart views can be panned back & forth and zoomed in & out, including specifying the exact X-Y coordinate range.

- 5. Properties of axes, traces, rides, charts, text & colors can be customized.

Numerical data is input to W-Edit in the form of plain or binary text files. Header & Comment information supplied by T-Spice is used for automatic chart configuration. Runtime update of results is made possible by linking W-Edit to a running simulation in T-Spice. W-Edit saves data with chart, trace, axis & environment settings in files with the WDB (W-Edit Database).

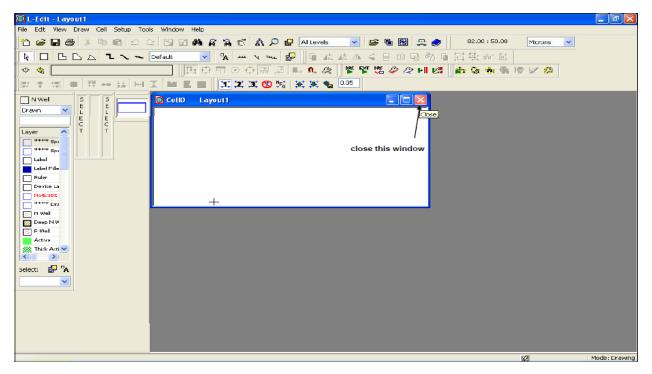

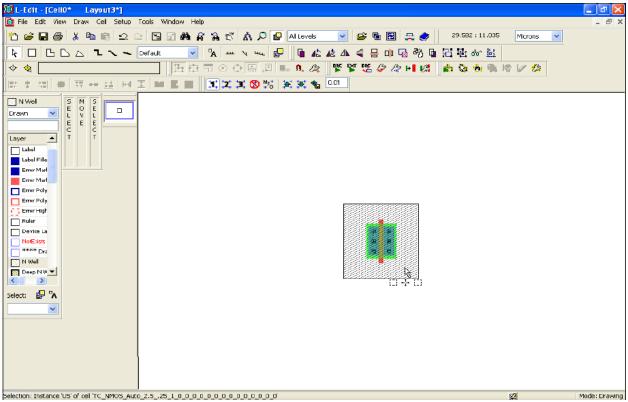

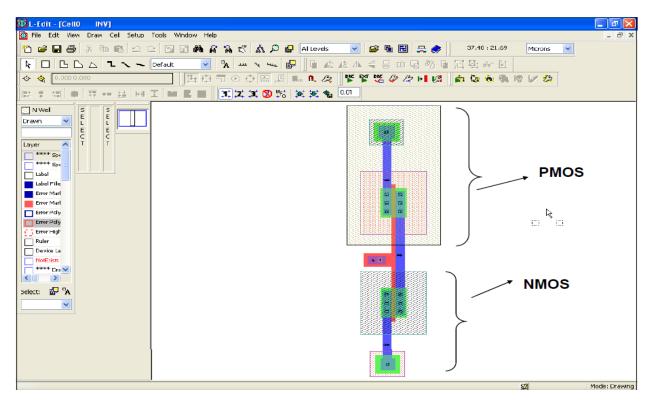

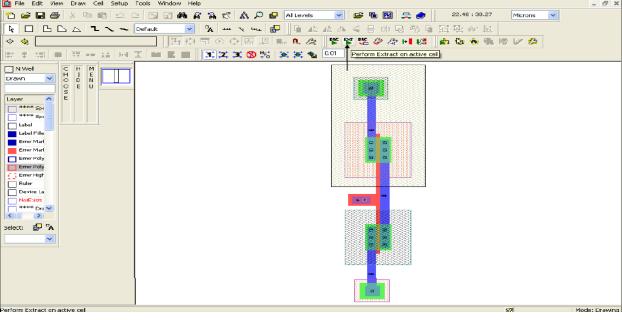

### **LAYOUT(L-EDIT)**

It is a tool that represents the masks that are used to fabricate an integrated circuit. It describes a layout design in terms of files, cells & mask primitives. On the layout level, the component parameters are totally different from schematic level. So it provides the facility to the user to analyze the response of the circuit before forwarding it to the time consuming & costly process of fabrication. There are rules for designing layout diagram of a schematic circuit using which user can compare the output response with the expected one.

### L- Edit: An Integrated Circuit Layout Tool

In L- Edit, layers are associated with masks used in the fabrication process. Different layers can be conveniently represented by different colors and patterns. L- Edit describes a layout design in terms of files, cells, instances, and mask primitives. You may load as many files as desired into memory. A file may be composed of any number of cells. A file may be composed of any number of cells. These cells may be hierarchically related, as in a typical design, or they may be independent, as in a library file. Cells may contain any number or combination of mask primitives and instances of other cells.

### **Cells: The Basic Building Blocks**

The basic building block of the integrated circuit design in L- Edit is a cell. Design layout occurs within cells. A cell can:

- ❖ Contain part or all of the entire design.

- ❖ Be referenced in other cells as a sub- cell, or instance.

- ❖ Be made up entirely of instances of other cells.

- Contain original drawn objects, or primitives.

- ❖ Be made up entirely of primitives or a combination of primitives and instances of other cells.

### **Hierarchy**

L- Edit supports fully hierarchical mask design. Cells may contain instances of other cells. An instance is a reference to a cell; should you edit the instanced cell, the change is reflected in all the instances of that cell. Instances simplify the process of updating a design, and also reduce data storage requirements, because an instance does not need to store all the data within the instanced cell instead, only a reference to the instanced cell is stored, along with information on the position of the instance and on how the instance may be rotated and mirrored.

L- Edit does not use a "separated" hierarchy: instances and primitives may coexist in the same cell at any level in the hierarchy. Design files are self- contained. The pointer to a cell contained in an instance always points to a cell within the same design file. When cells are copied from one file to another, L- Edit automatically copies across any cells that are instanced by the copied cell, to maintain the self- contained nature of the destination file.

### **Design Rules**

Manufacturing constraints can be defined in L- Edit as design rules. Layouts can be checked against these design rules.

### **Design Features**

L- Edit is a full- custom mask editor. Manual layout can be accomplished more quickly because of L Edit's intuitive user interface. In addition, one can construct special structures to utilize a technology without, worrying about problems caused by automatic transformations. Phototransistors, guard bars, vertical and horizontal bipolar transistors, static structures, and Schottky diodes, for example, are as easy to design in CMOS- Bulk technology as are conventional MOS transistors.

### Floor plans

L- Edit is a manual floor planning tool. You have the choice of displaying instances in outline, identified only by name, or as fully fleshed- out mask geometry. When you display your design in outline, you can manipulate the arrangement of the cells in your design quickly and easily to achieve the desired floor plan. One can manipulate instances at any level in the hierarchy, with insides hidden or displayed, using the same graphical move/select operations or rotation/ mirror commands that you use on primitive mask geometry.

### **Memory Limits**

In L- Edit, one can make your design files as large as one like, given available RAM and disk space.

### Hard Copy

L- Edit provides the capability to print hard copy of the design. A multiage option allows very large plots to

be printed to a specific scale on multiple 8 1/2 x 11 inch pages. An L- Edit macro is available to support large- format, high- resolution, color plotting on inkjet plotters.

### Variable Grid

L- Edit's grid options support lambda- based design as well as micron- based and mil- based design.

### **Error Recovery**

L- Edit's error- trapping mechanism catches system errors and in most cases provides a means to recover without losing or damaging data.

### L- Edit Modules

- ❖ L- Edit <sup>TM</sup>: a layout editor

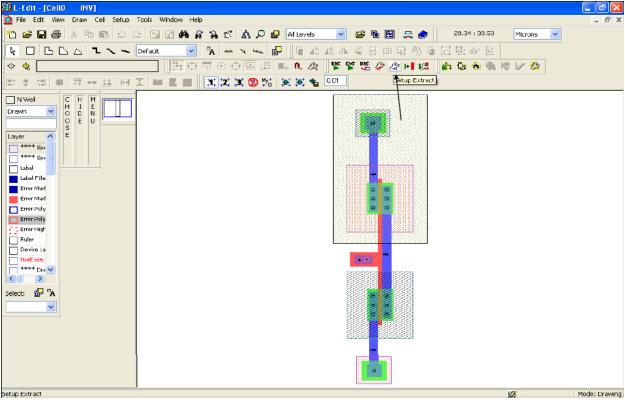

- ❖ L- Edit ¤ Extract TM: a layout extractor

- ❖ L- Edit ¤ DRC <sup>TM</sup>: a design rule checker

L- Edit is a full- featured, high-performance, interactive, graphical mask layout editor. L- Edit generates layouts quickly and easily, supports fully hierarchical designs, and allows an unlimited number of layers, cells, and levels of hierarchy. It includes all major drawing primitives and supports 90°, 45°, and all- angle drawing modes.

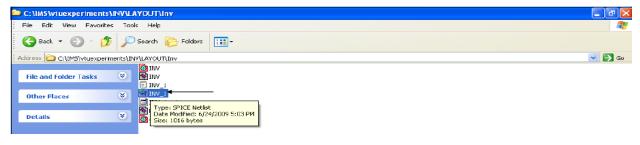

L- Edit ¤ Extract creates SPICE- compatible circuit netlists from L- Edit layouts. It can recognize active and passive devices, sub circuits, and the most common device parameters, including resistance, capacitance, device length, width, and area, and device source and drain area.

L- Edit ¤ DRC features user- programmable rules and handles minimum width, exact width, minimum space, minimum surround, non- exist, overlap, and extension rules. It can handle full chip and region- only DRC. DRC offers Error Browser and Object Browser functions for quickly and easily cycling through rule-checking errors.

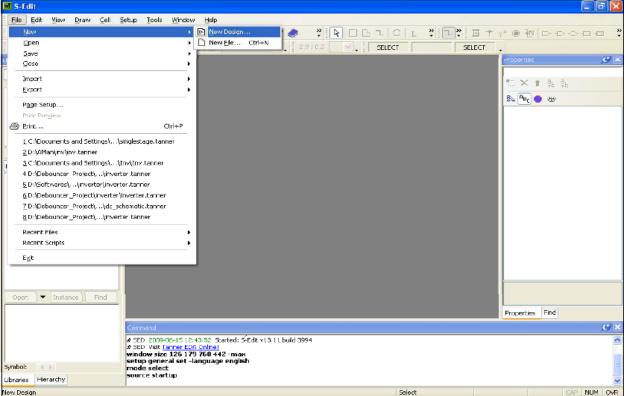

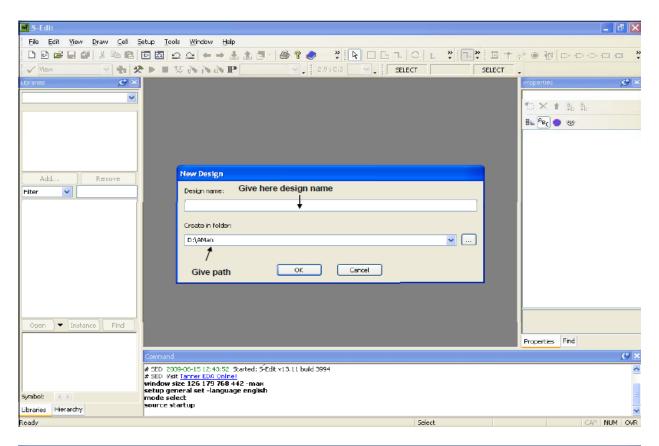

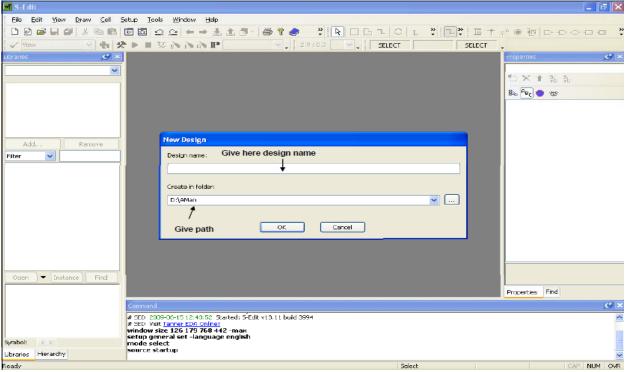

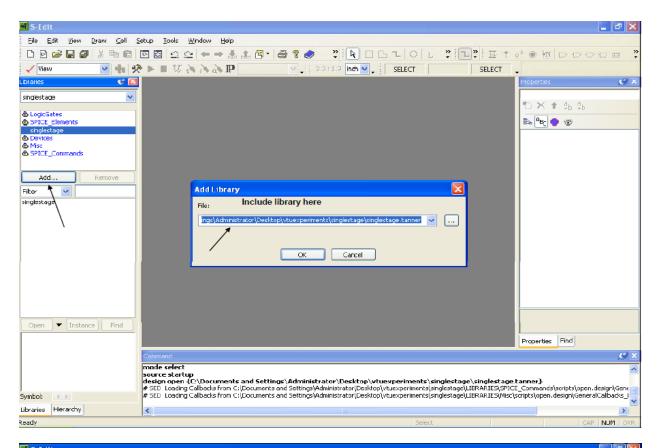

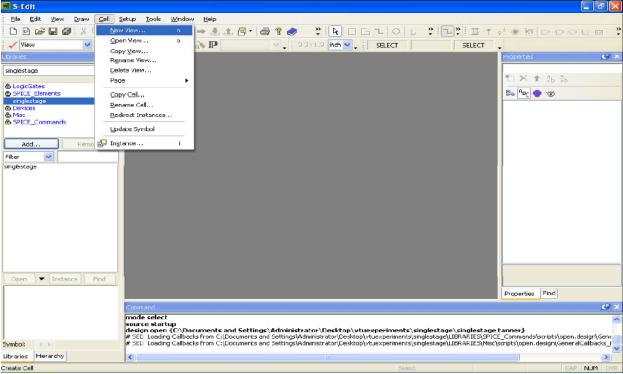

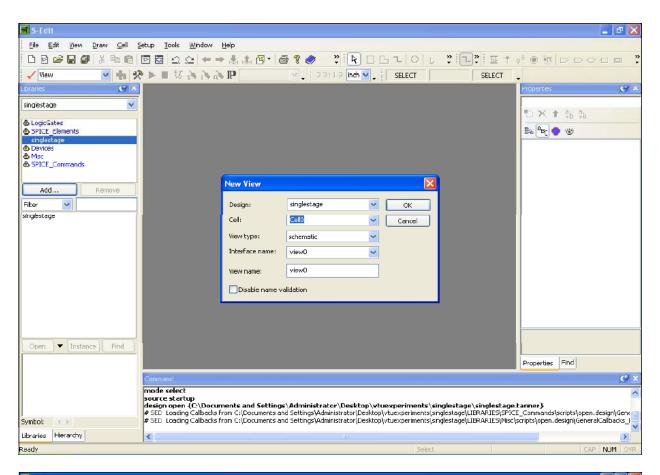

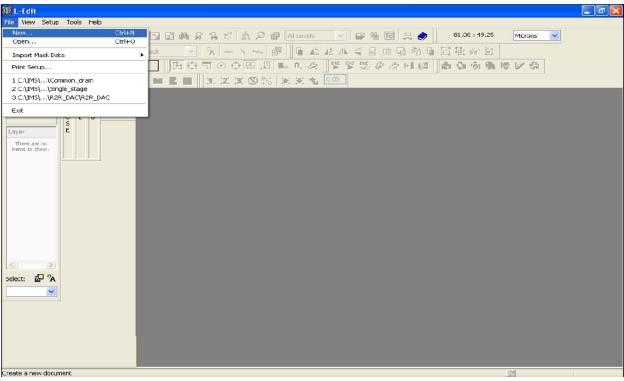

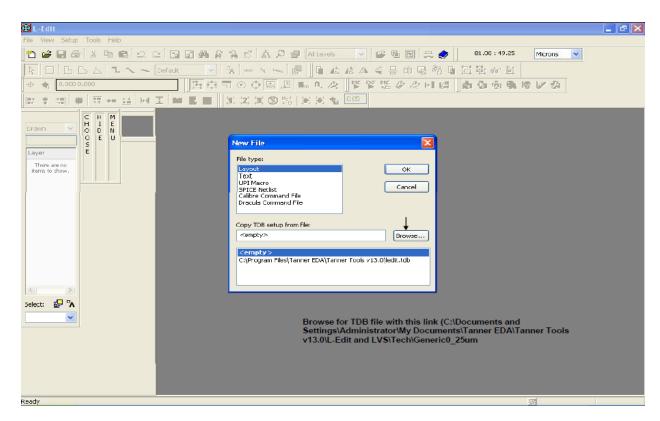

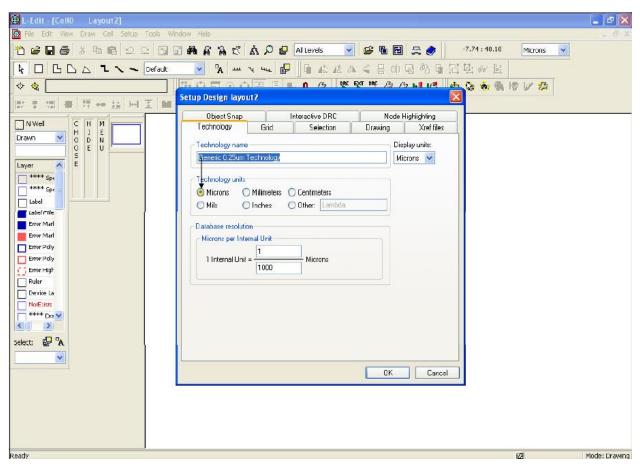

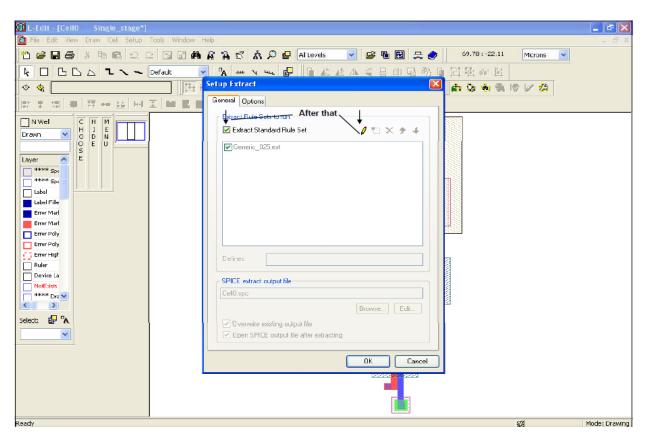

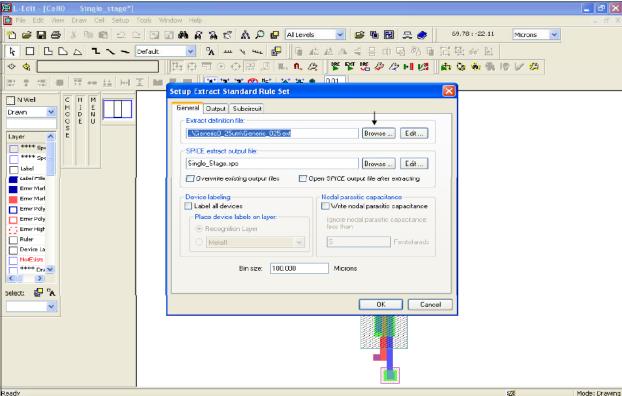

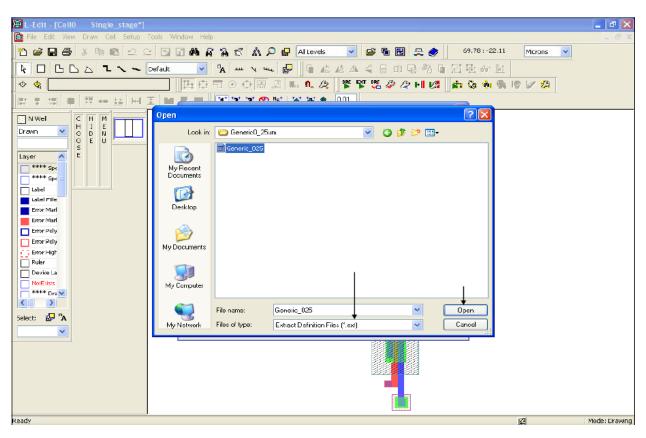

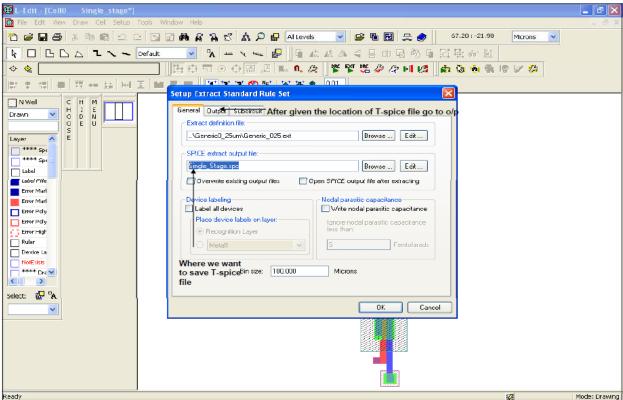

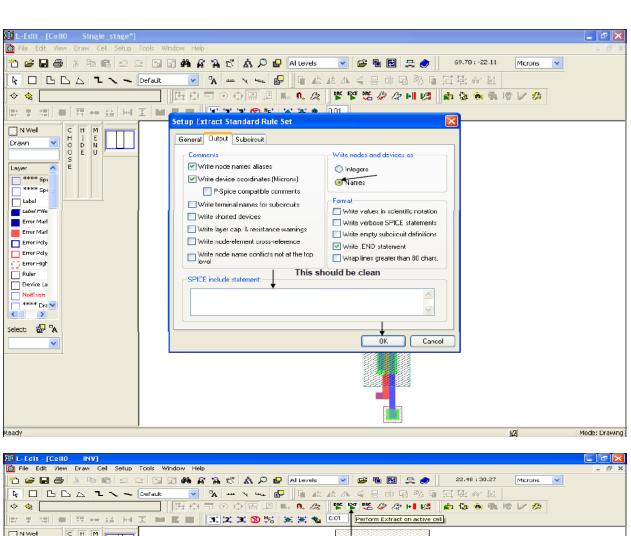

# **Steps to use Tanner tool:**

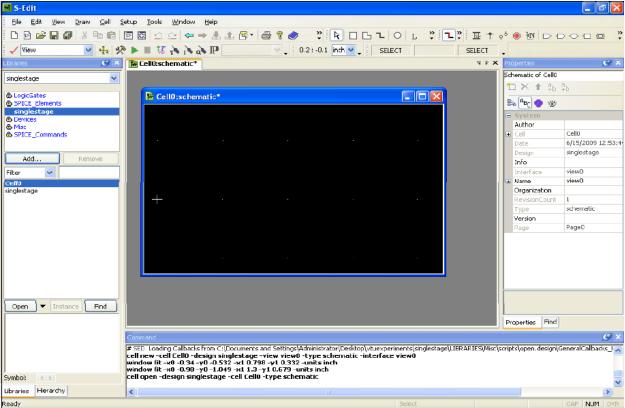

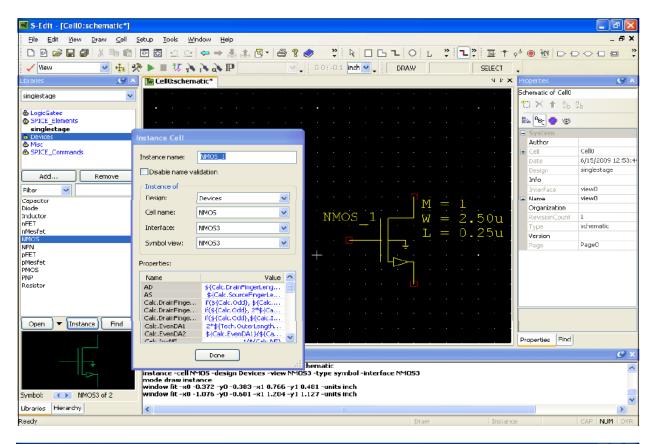

## i.SCHEMATIC (S-edit):

Start the tanner EDA by using the desktop shortcut or by using the

➤ Start → Programs → tanner EDA → tanner tool v13.0 → S-edit.

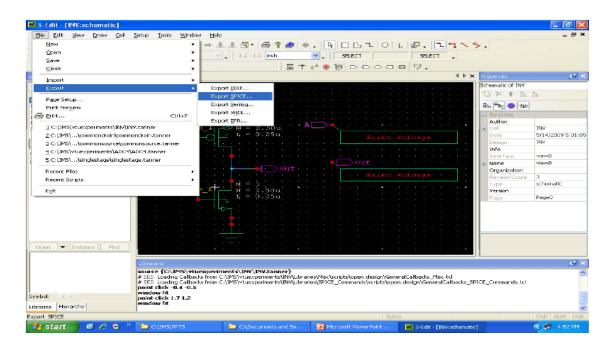

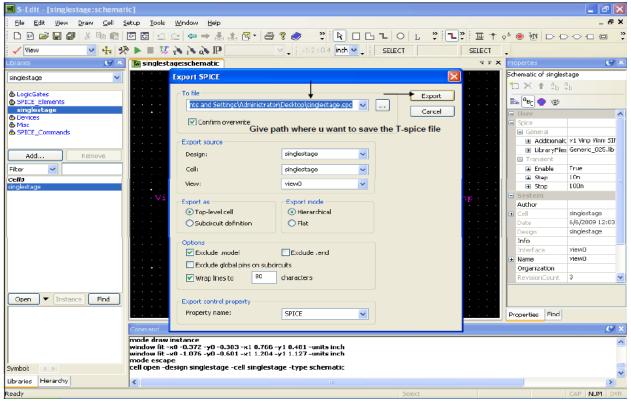

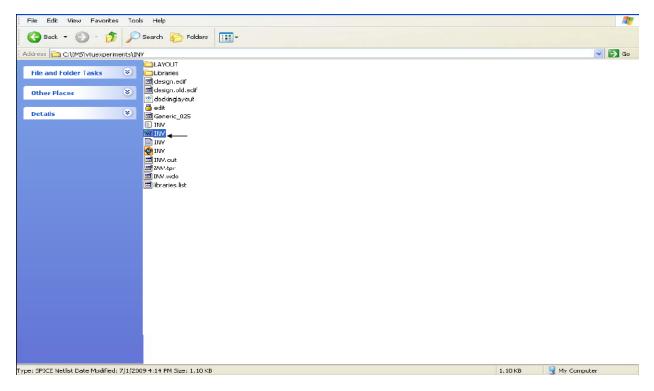

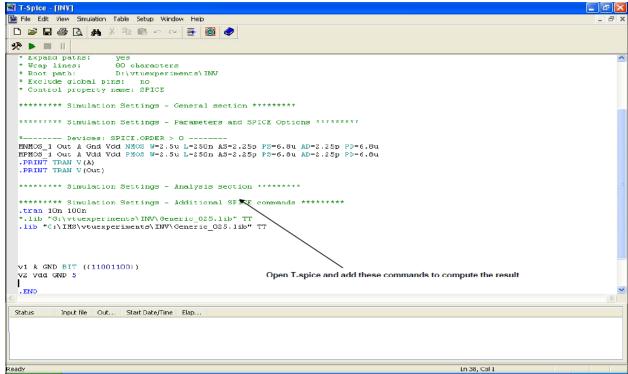

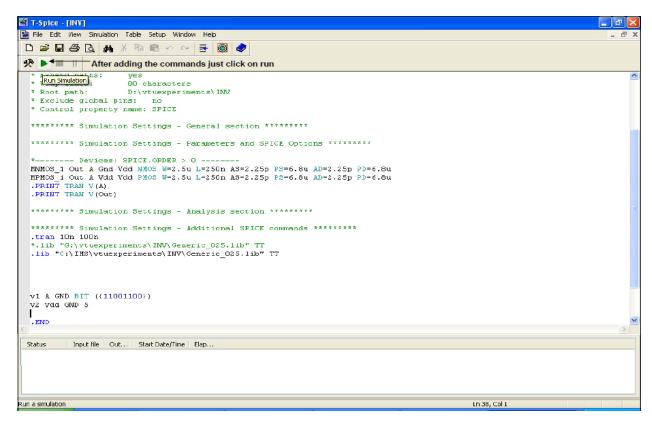

### After completion of the design just export T-spice

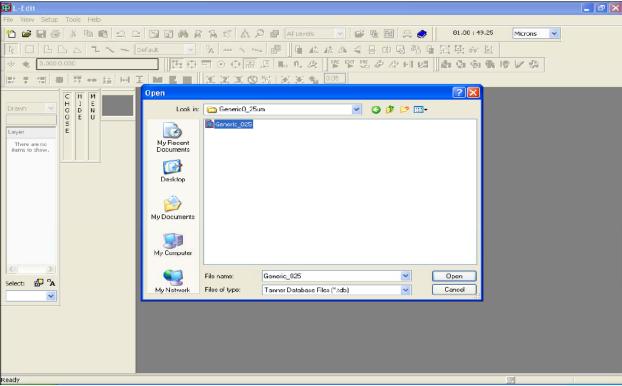

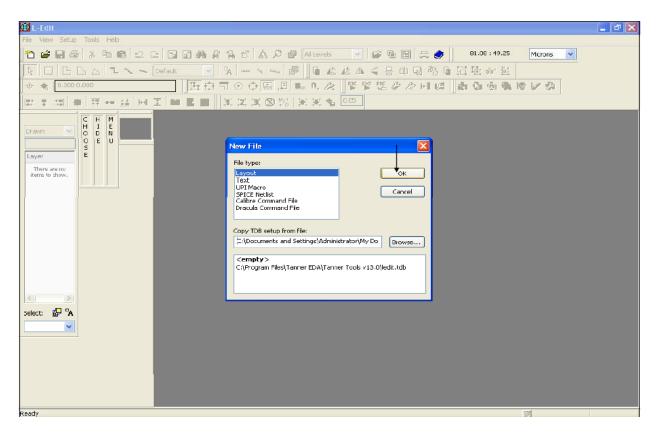

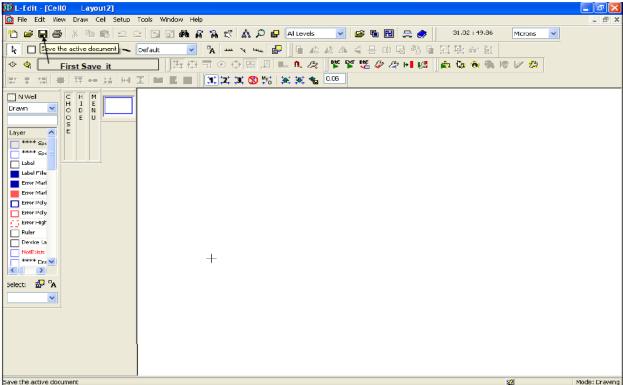

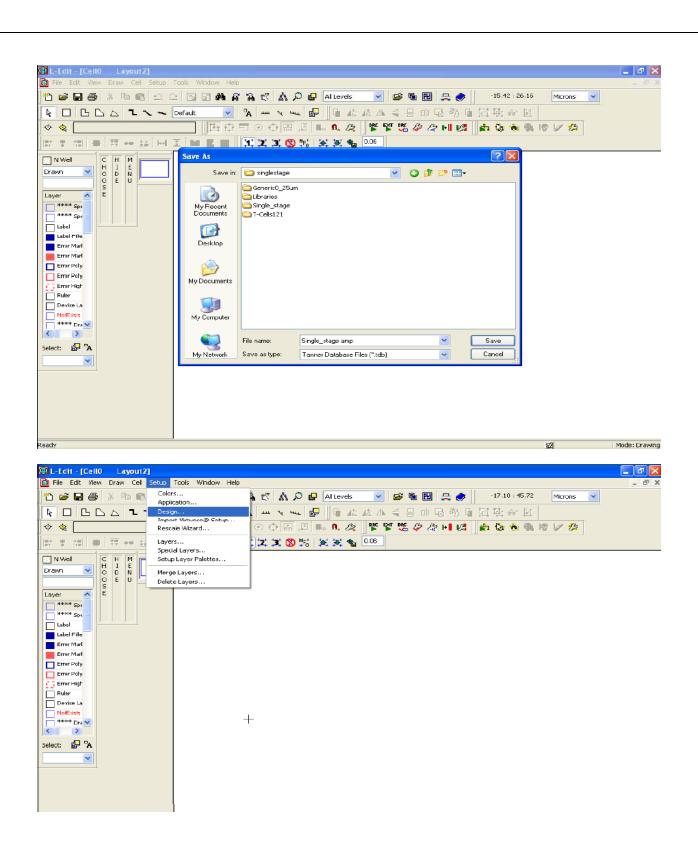

# ii) Layout (L-edit):

Start  $\rightarrow$  Programs  $\rightarrow$  tanner EDA  $\rightarrow$ tanner tool v13.0  $\rightarrow$  L-edit

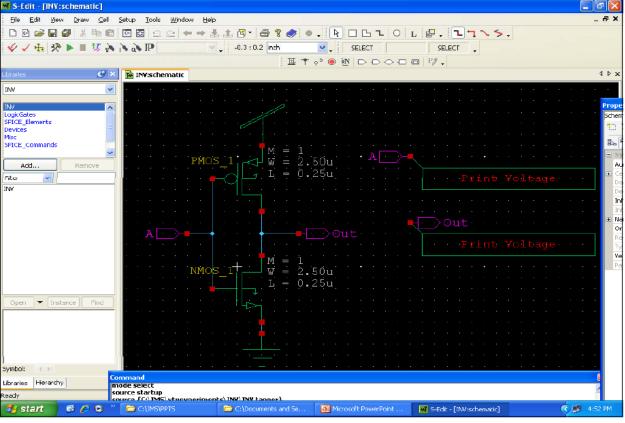

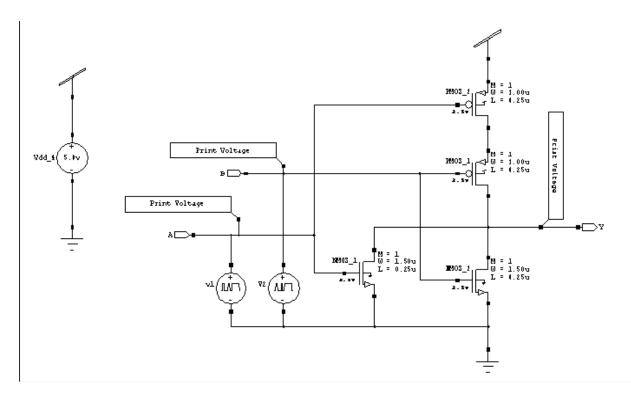

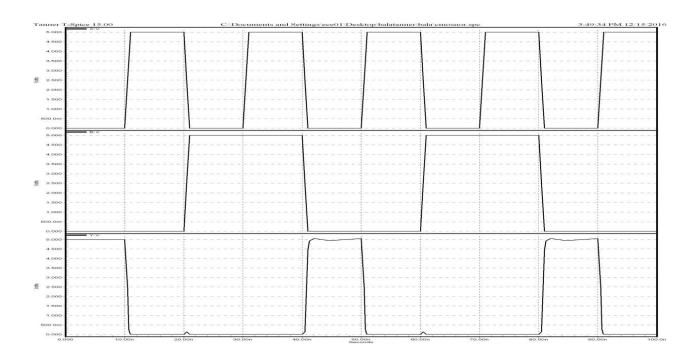

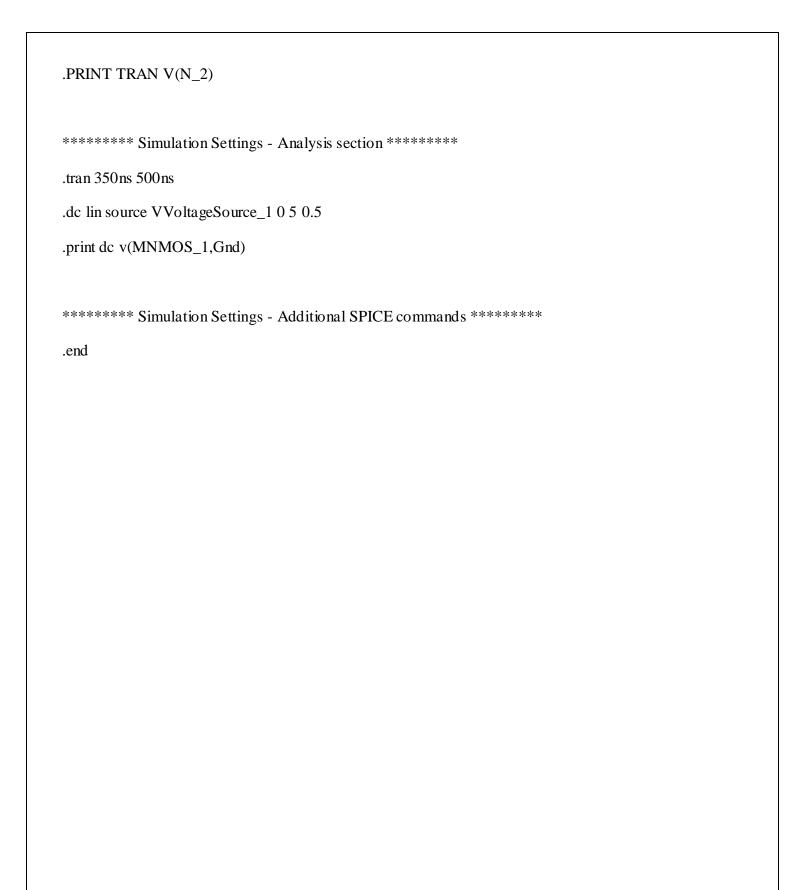

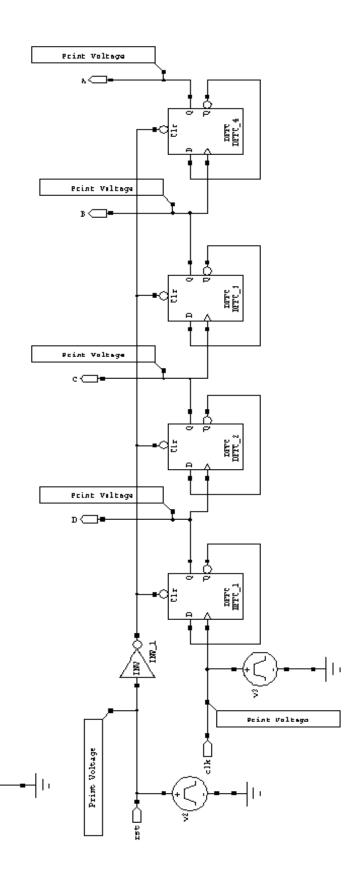

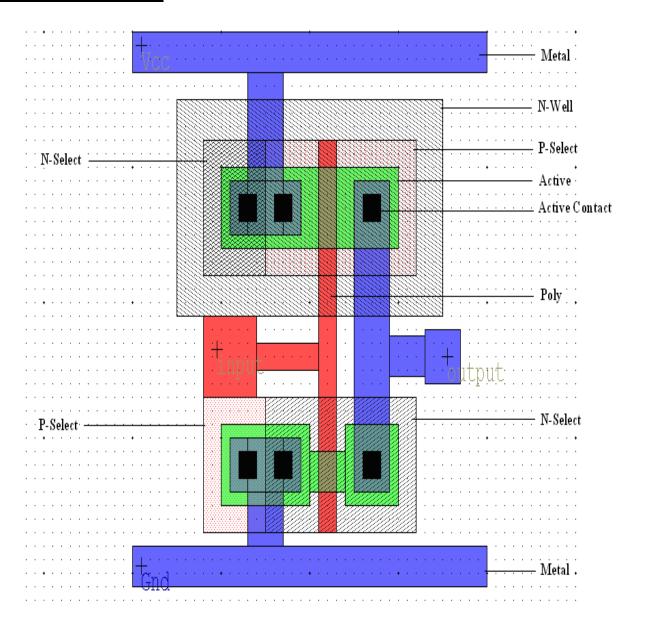

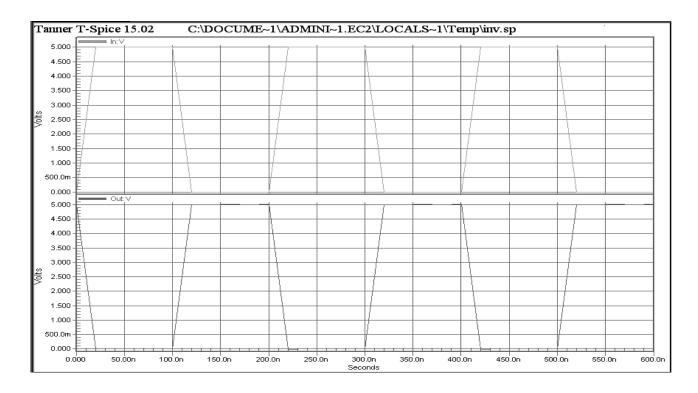

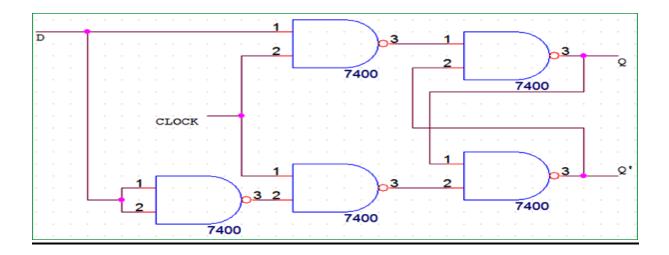

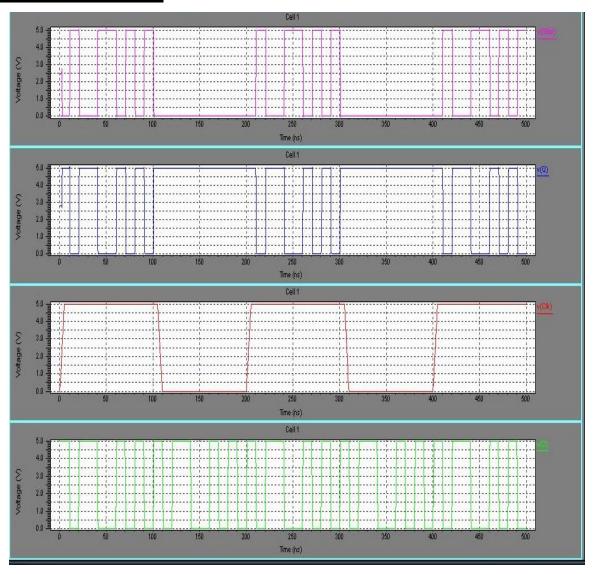

| EXP.NO: | DESIGN AND SIMULATION OF CMOS GATES |

|---------|-------------------------------------|

| DATE:   |                                     |

To perform the functional verification of the CMOS gates through schematic entry.

#### FACILITIES REQUIRED AND PROCEDURE

#### a) Facilities required to do the experiment

| S.No. | SOFTWARE REQUIREMENTS                     | QUANTITY |

|-------|-------------------------------------------|----------|

| 1     | S-Edit, W-Edit, T-Edit using Tanner Tool. | 1        |

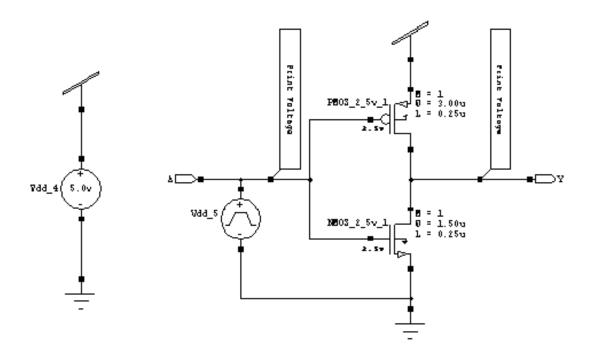

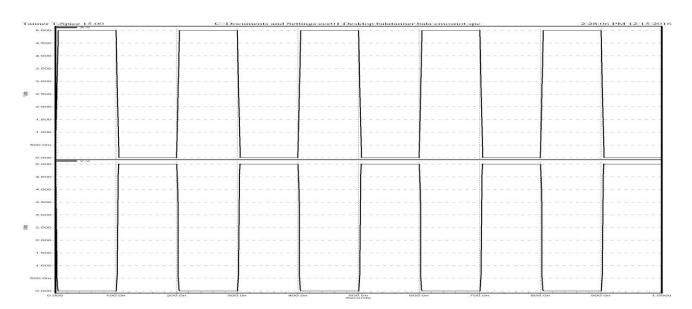

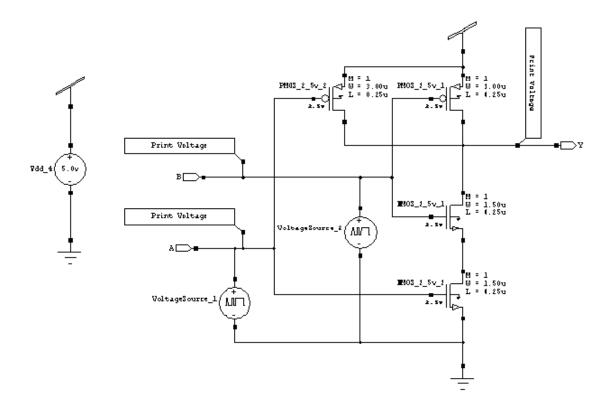

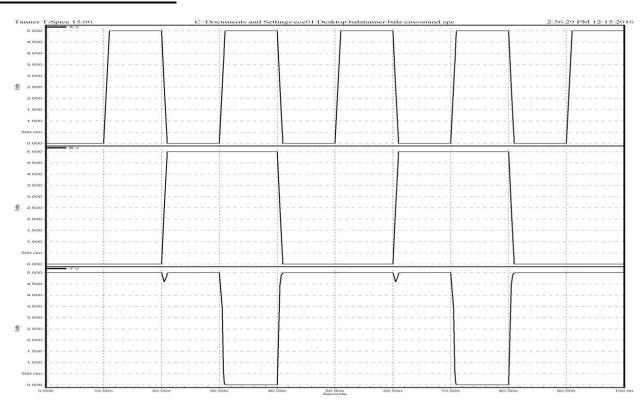

#### b) Procedure for doing the experiment